华硕K42JR时序分析

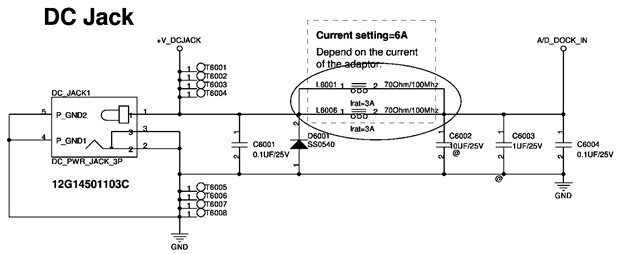

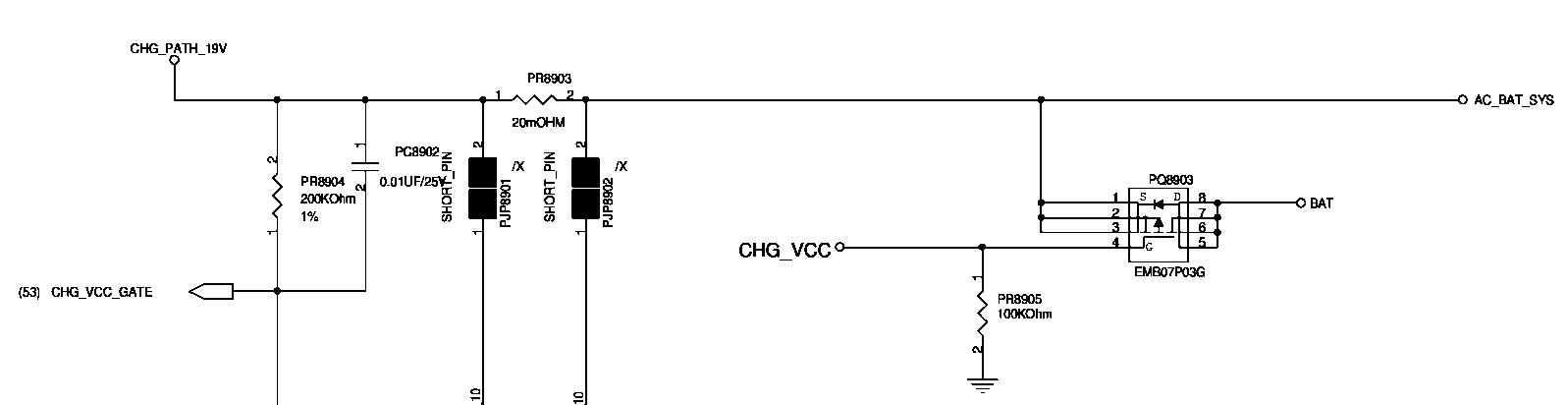

首先是适配器插入,输出A/D_DOCK_IN

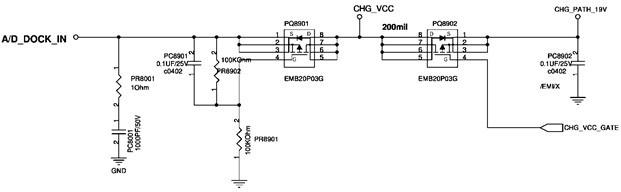

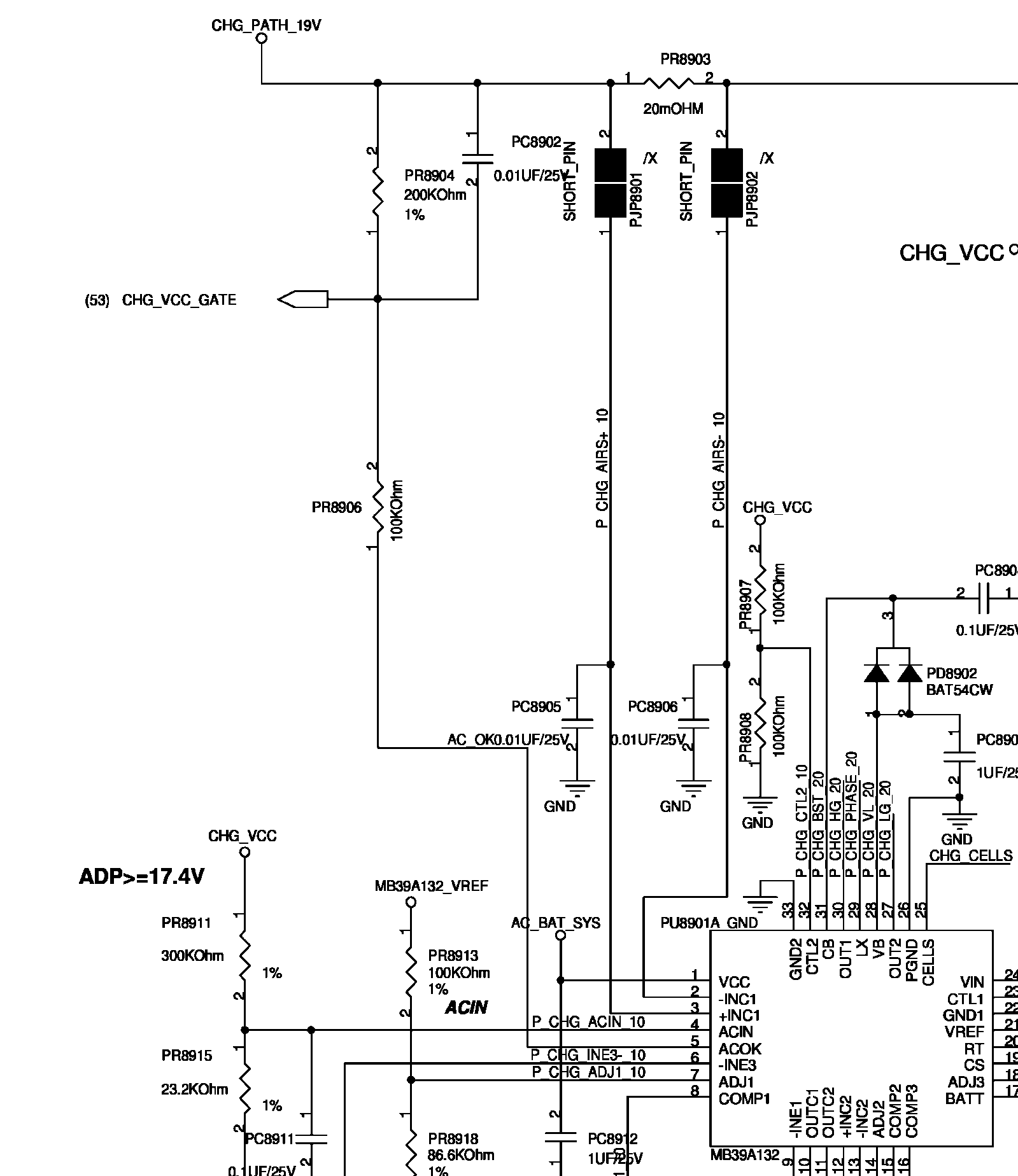

A/D_DOCK_IN送给PQ8901的S极,同时经过PR8902和PR8901的分压成9.5v控制PQ8901直接导通产生CHG_VCC

CHG_VCC先经过PQ8902的体二极管产生小电流的CHG_PATH_19V。如果要完全导通PQ8902产生大电流的CHG_PATH_19V,需要相对低电平的CHG_VCC_GATE。

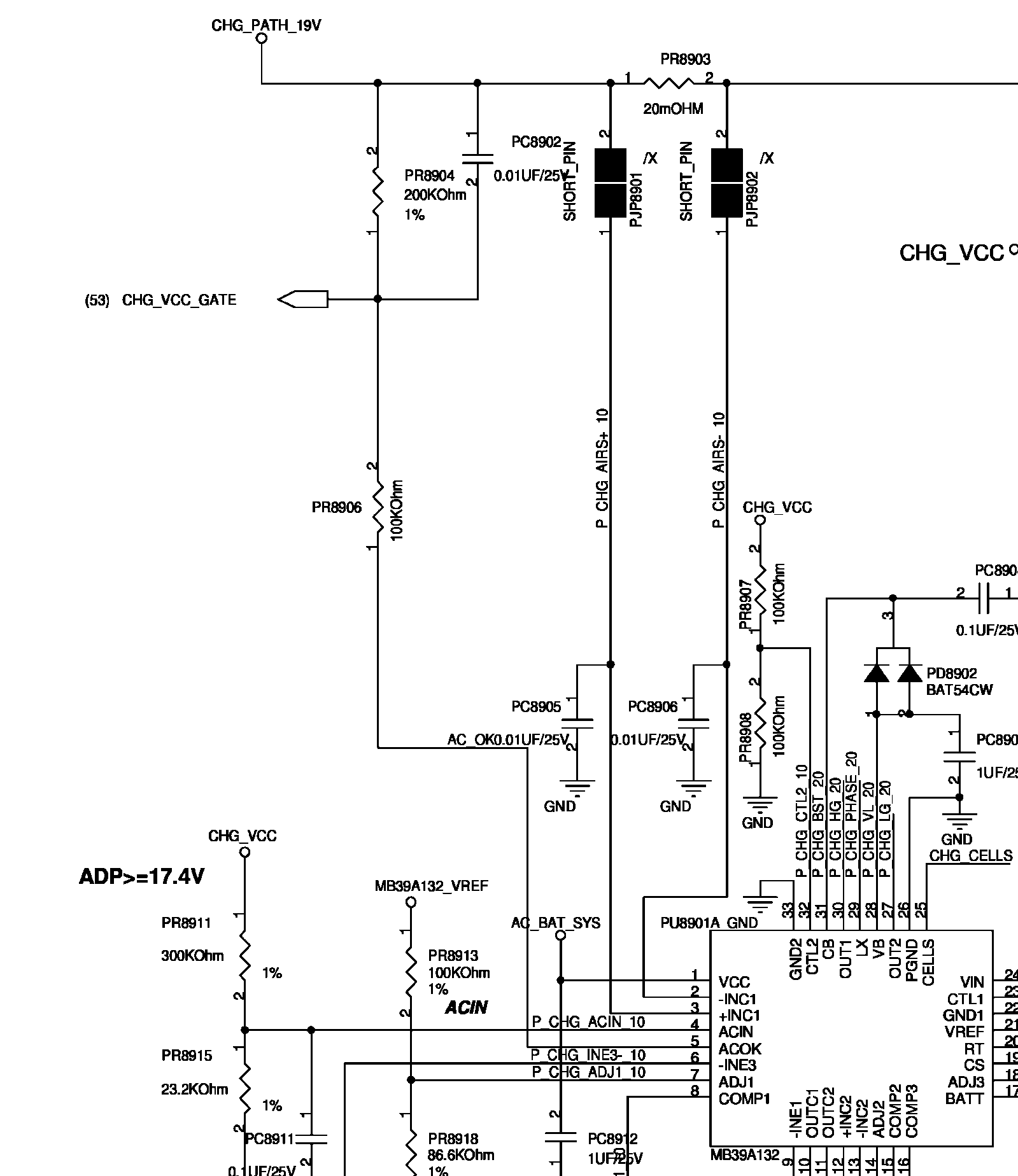

CHG_VCC_GATE的来源于充电芯片MB39A132的ACOK脚。ACOK需要输出低电平,才会使CHG_PATH_19经过PR8904和PR8906分压得到6v左右的相对低电平。

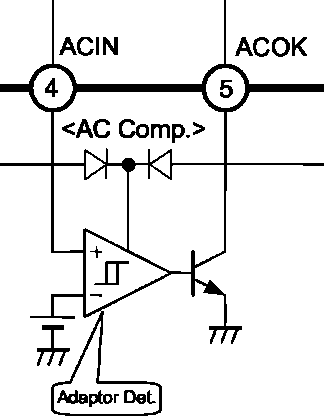

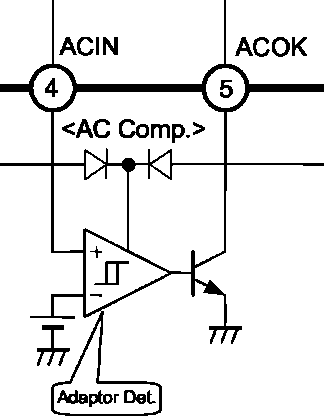

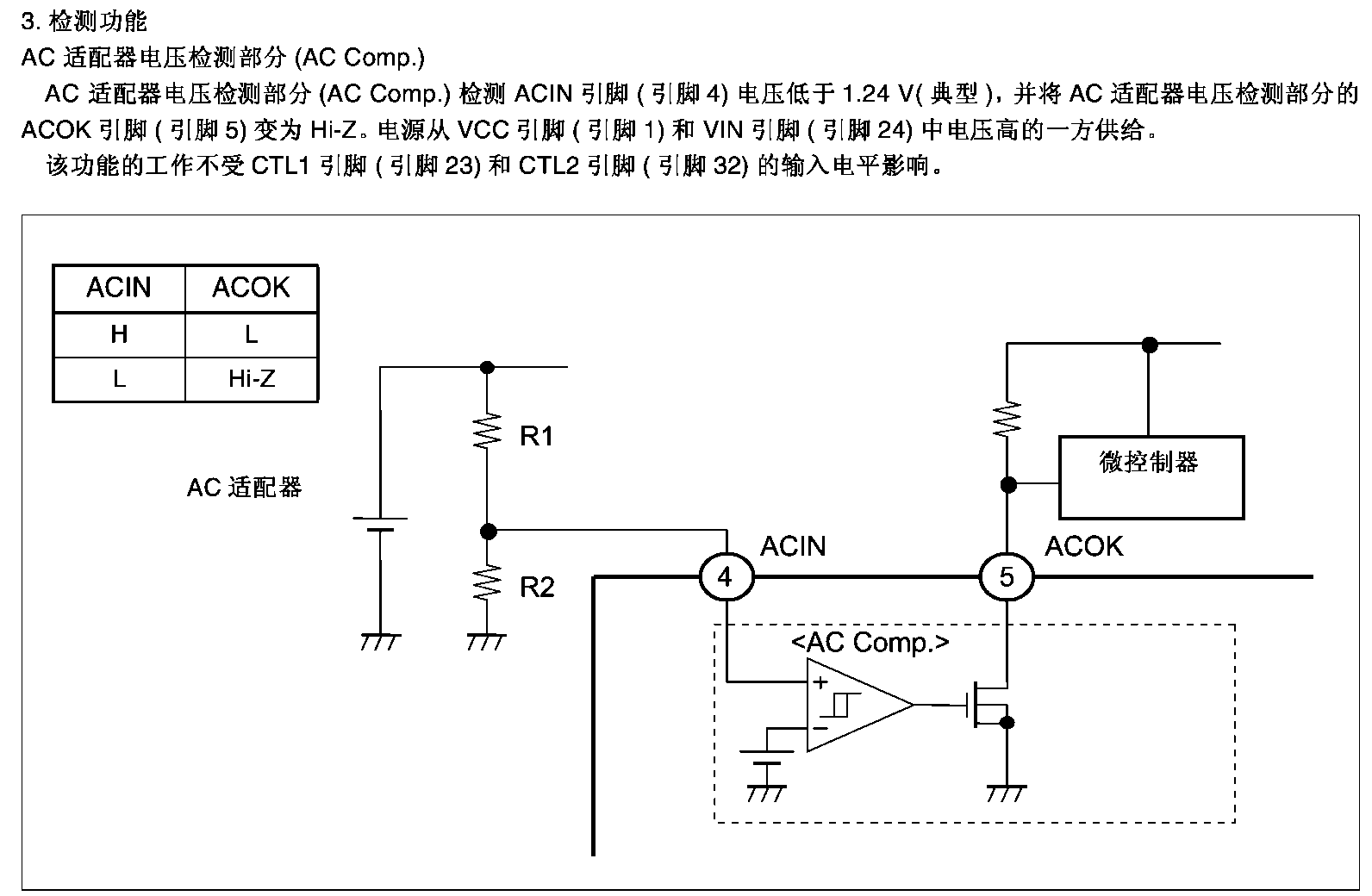

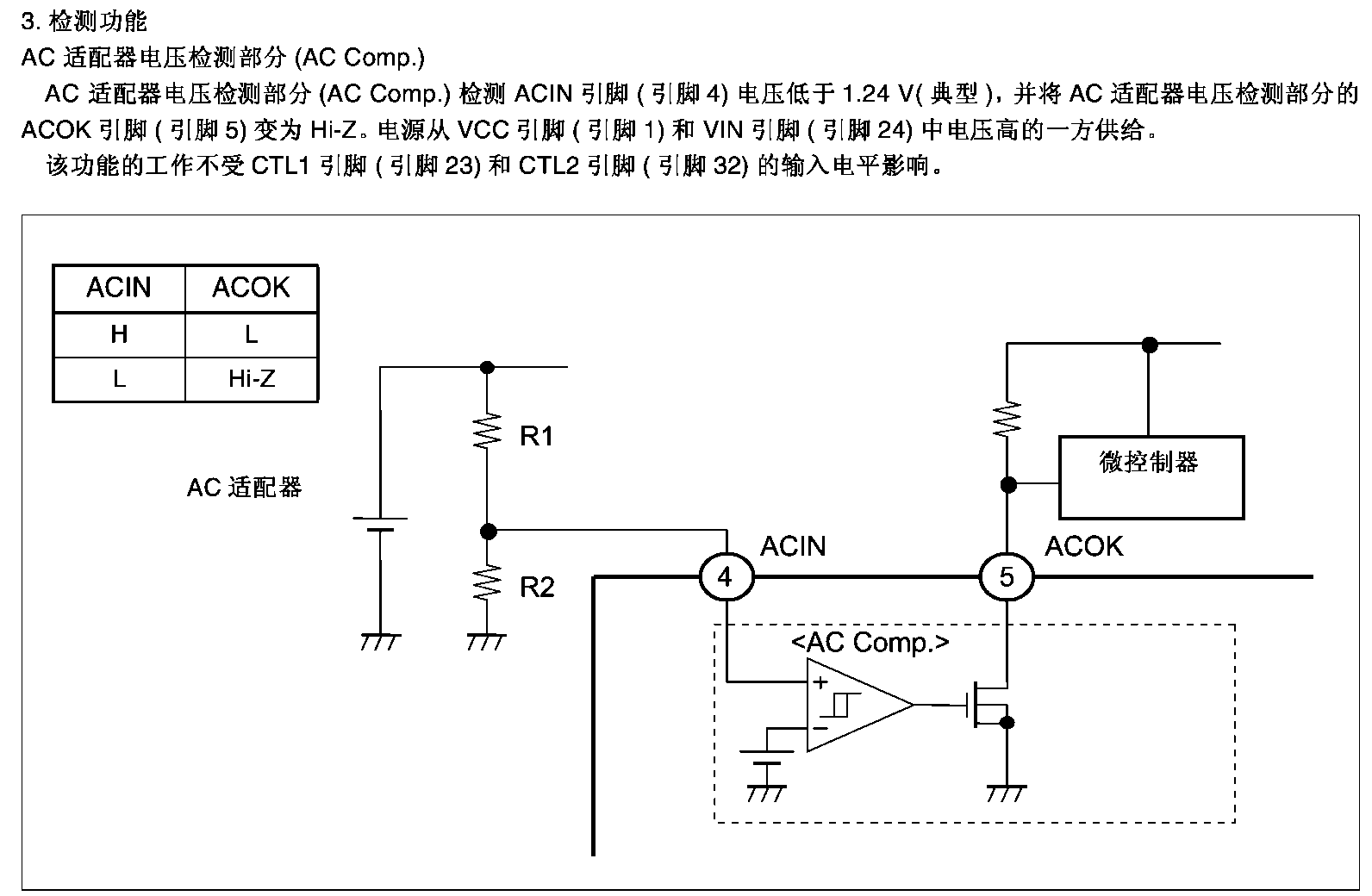

从MB39A132的内部框图得知,ACOK要输出低电平,必须内部的比较器输出高电平导通NPN三极管。也就是ACIN要高于适配器检测门槛电压值。

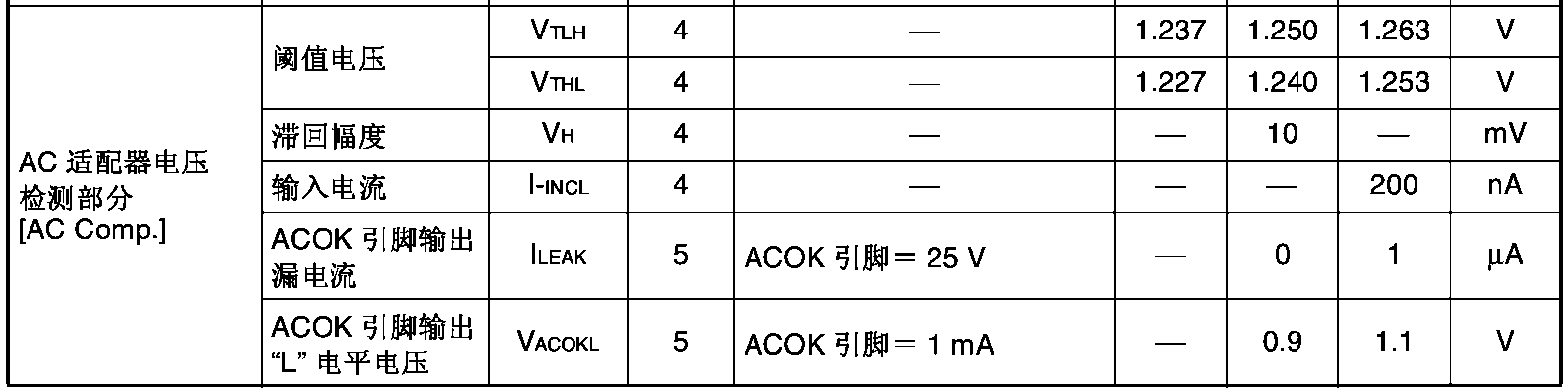

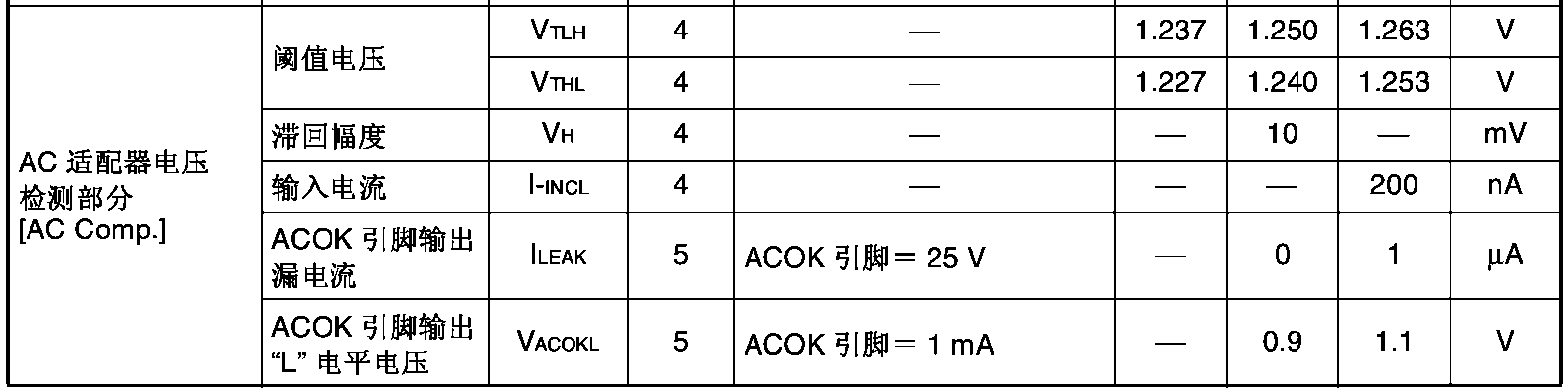

这个电压值为:1.25V(上升沿),MB39A132的数据手册中数据如下:

ACIN和ACOK的关系描述如下:

也就说只要ACIN超过1.25v,ACOK就会输出低电平。

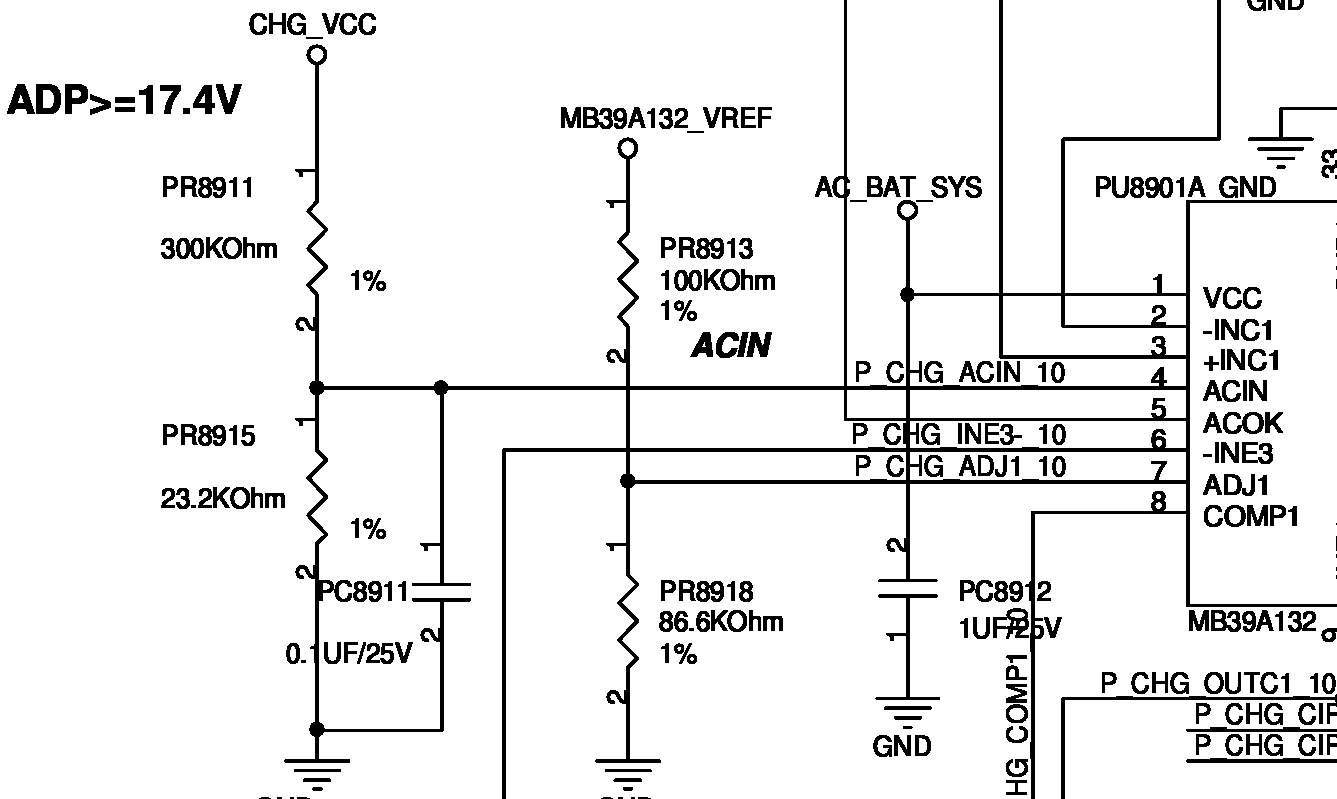

在K42JR中,ACIN是由CHG_VCC经过PR8911和PR8915分压后的来,经过计算,CHG_VCC电压不低于17.4V,ACOK将会输出低电平。

在K42JR中,ACIN是由CHG_VCC经过PR8911和PR8915分压后的来,经过计算,CHG_VCC电压不低于17.4V,ACOK将会输出低电平。

低电平的ACOK会使CHG_VCC_GATE分压成立,PQ8902导通,产生大电流的CHG_PATH_19V,经过PR8903产生公共点电压AC_BAT_SYS。同时CHG_VCC会加到PQ8903的G极,PQ8903截止,电池被隔离。

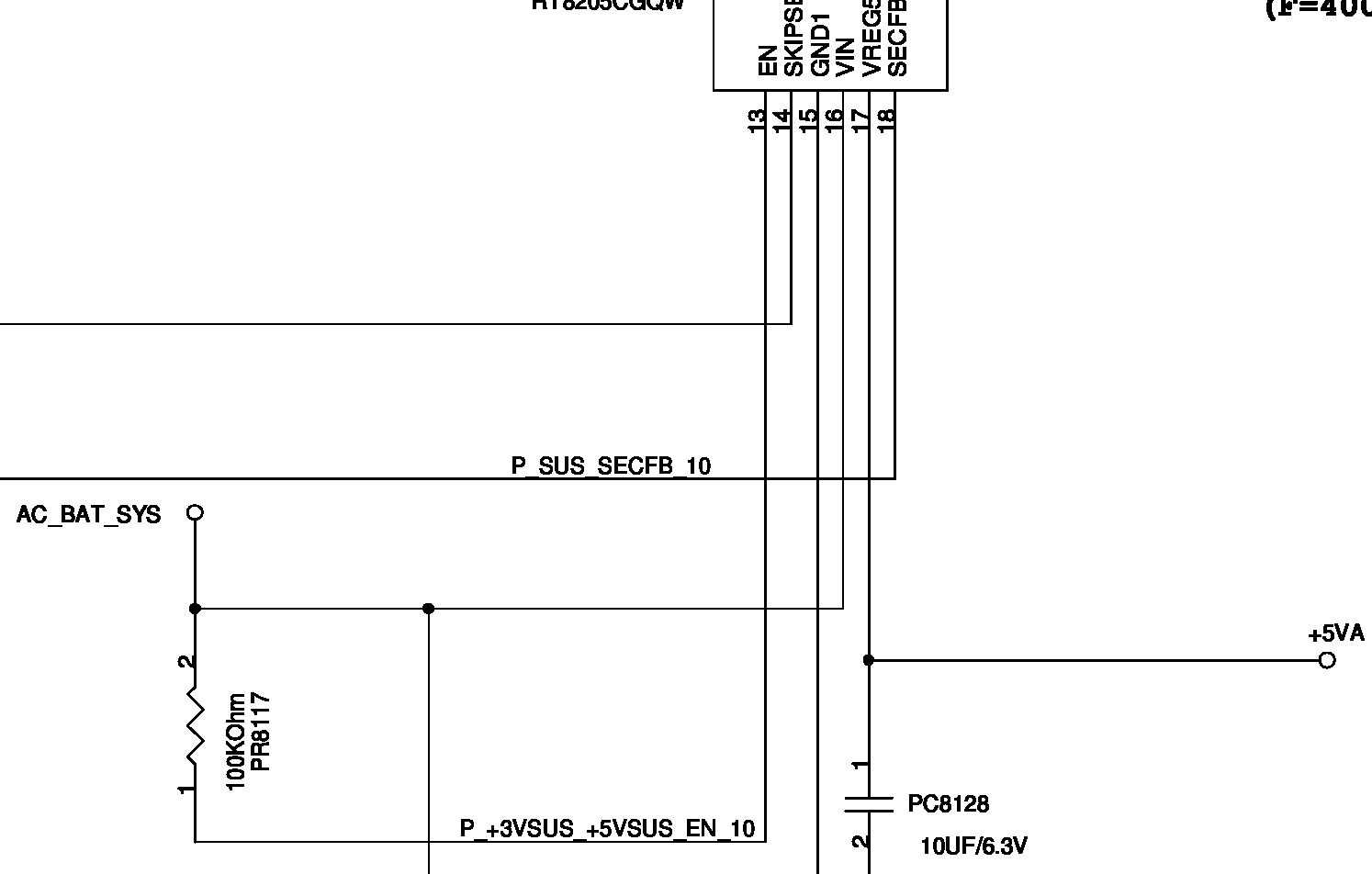

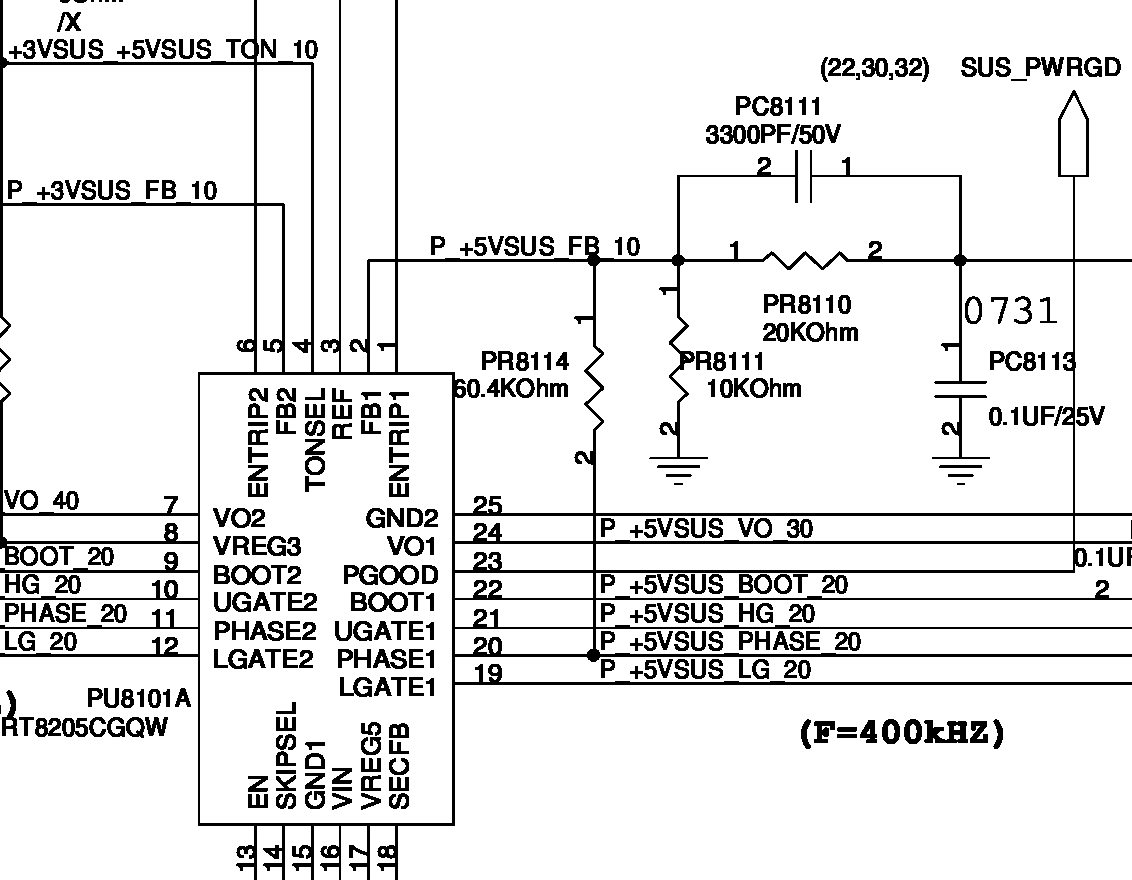

AC_BAT_SYS进RT8205的VIN,经过PR8117进入EN脚,开启VREG3、VREG5、REF电压。

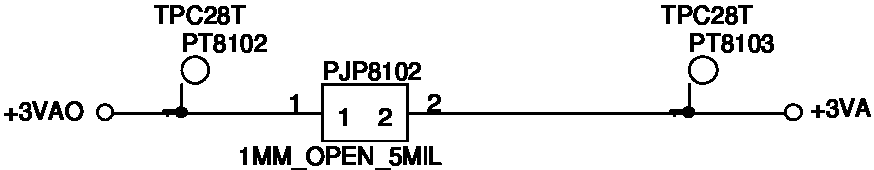

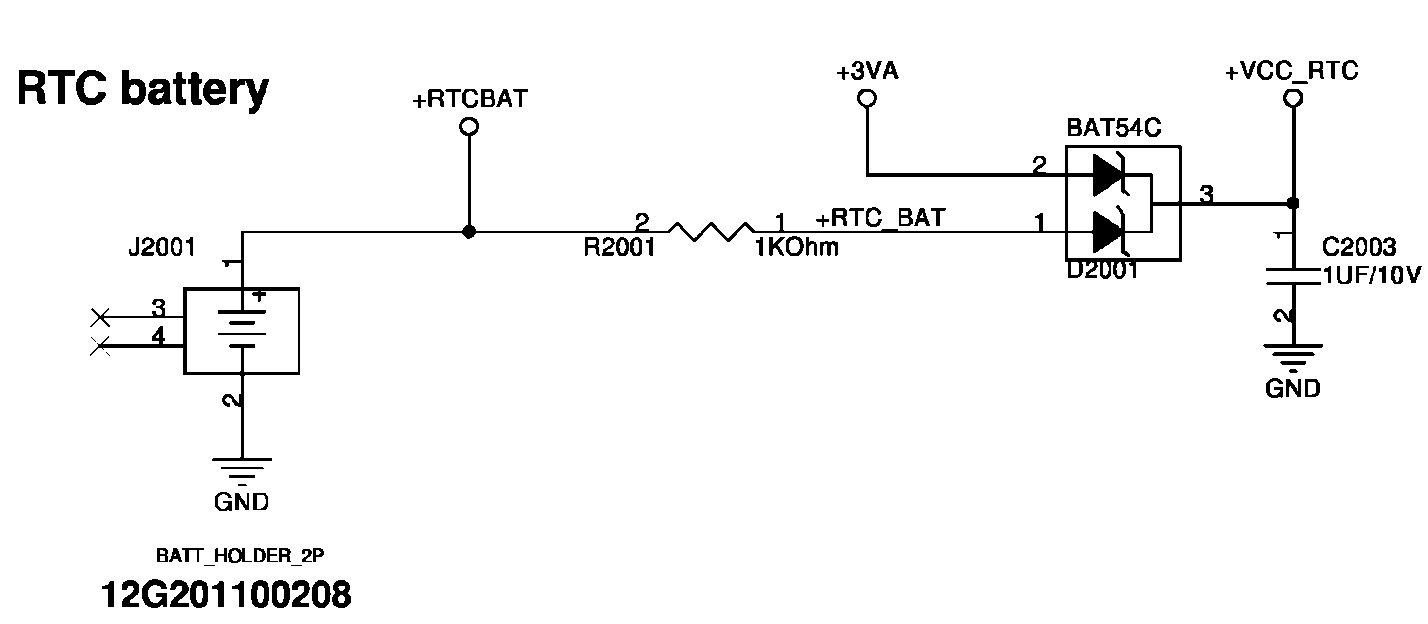

VREG3输出的+3VAO,过跳线更名为+3VA

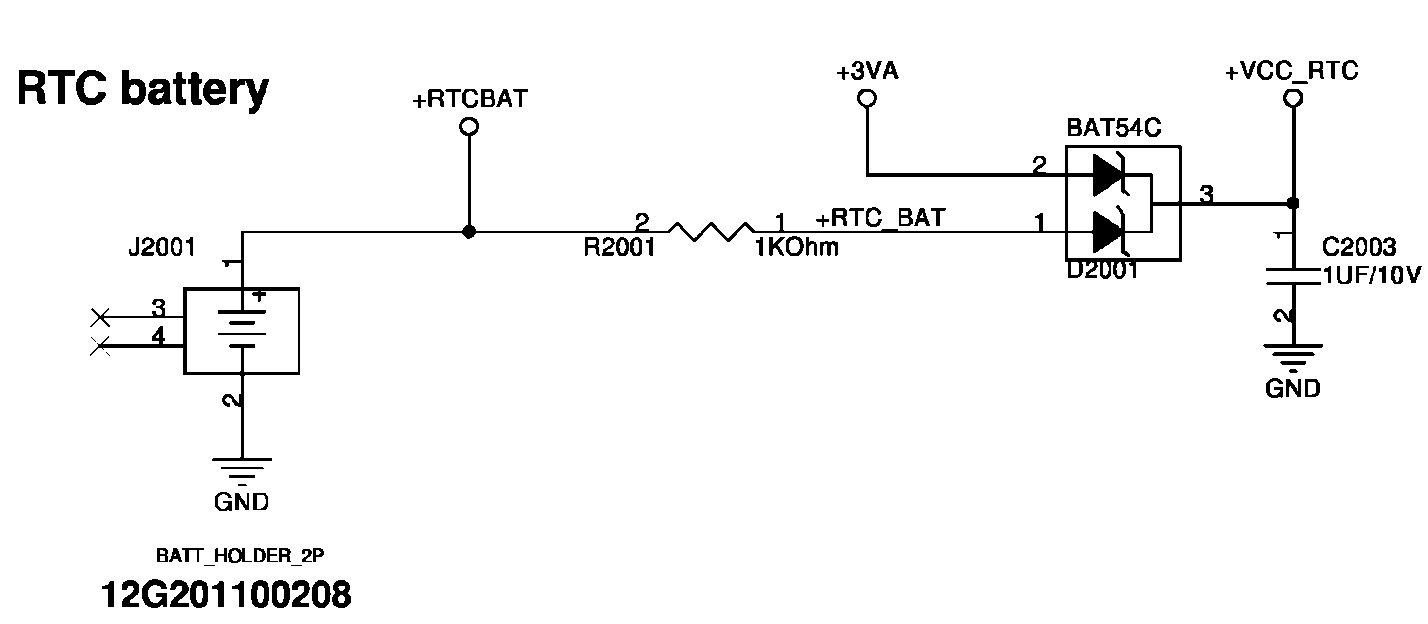

一路经D2001取代CMOS电池产生+VCC_RTC供至PCH的RTC电路。

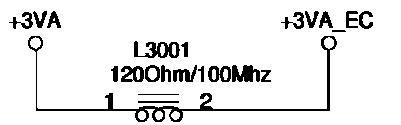

另一路经电感L3001产生+3VA_EC

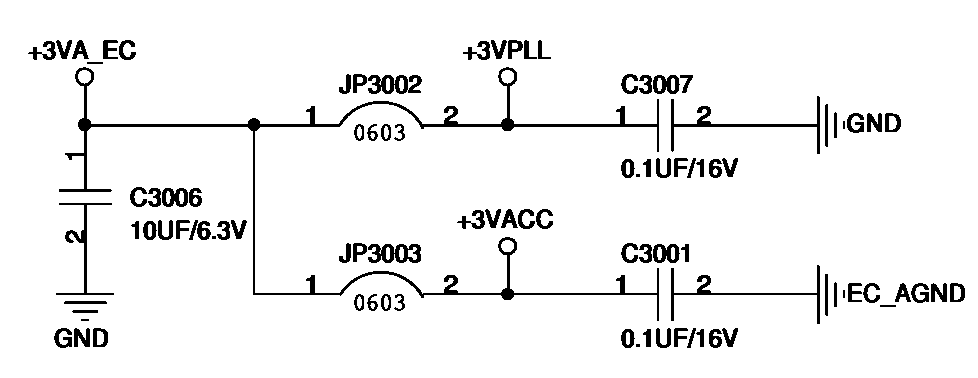

+3VA_EC再经过JP3003更名为_3VACC

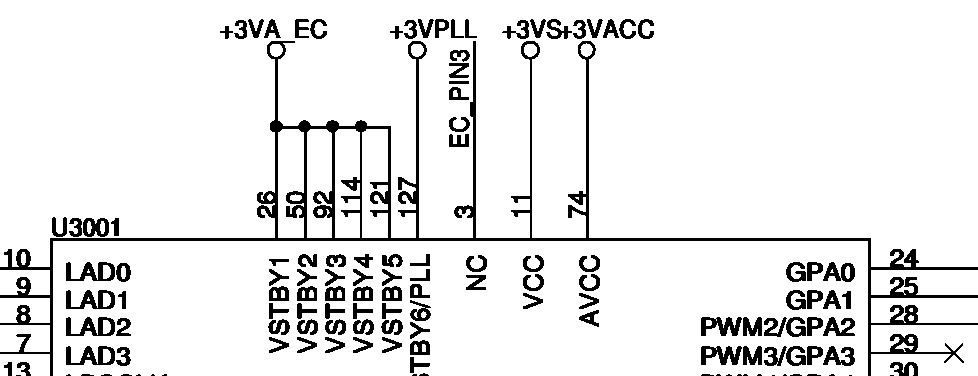

+3VA_EC给EC的74脚提供待机电压

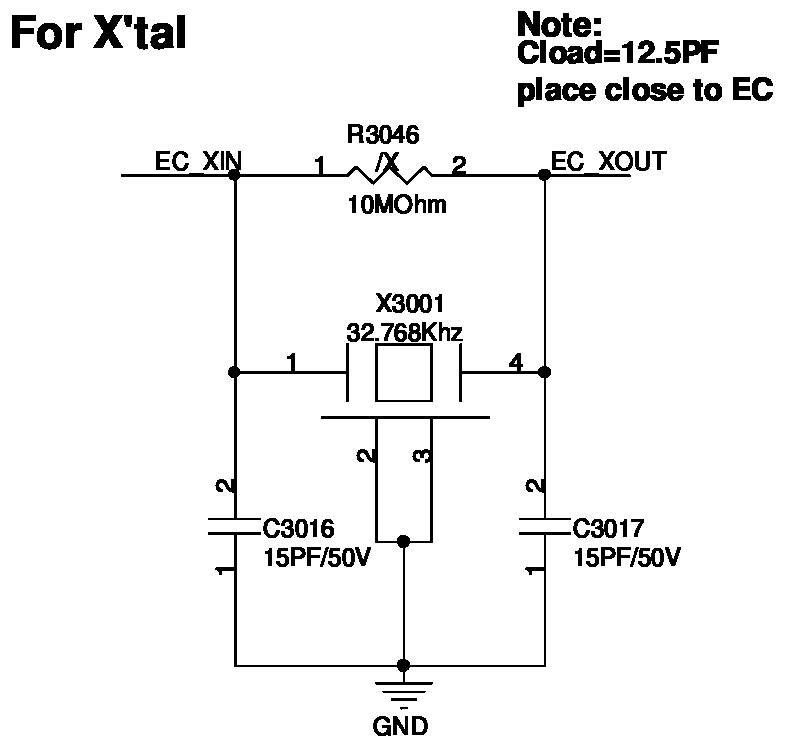

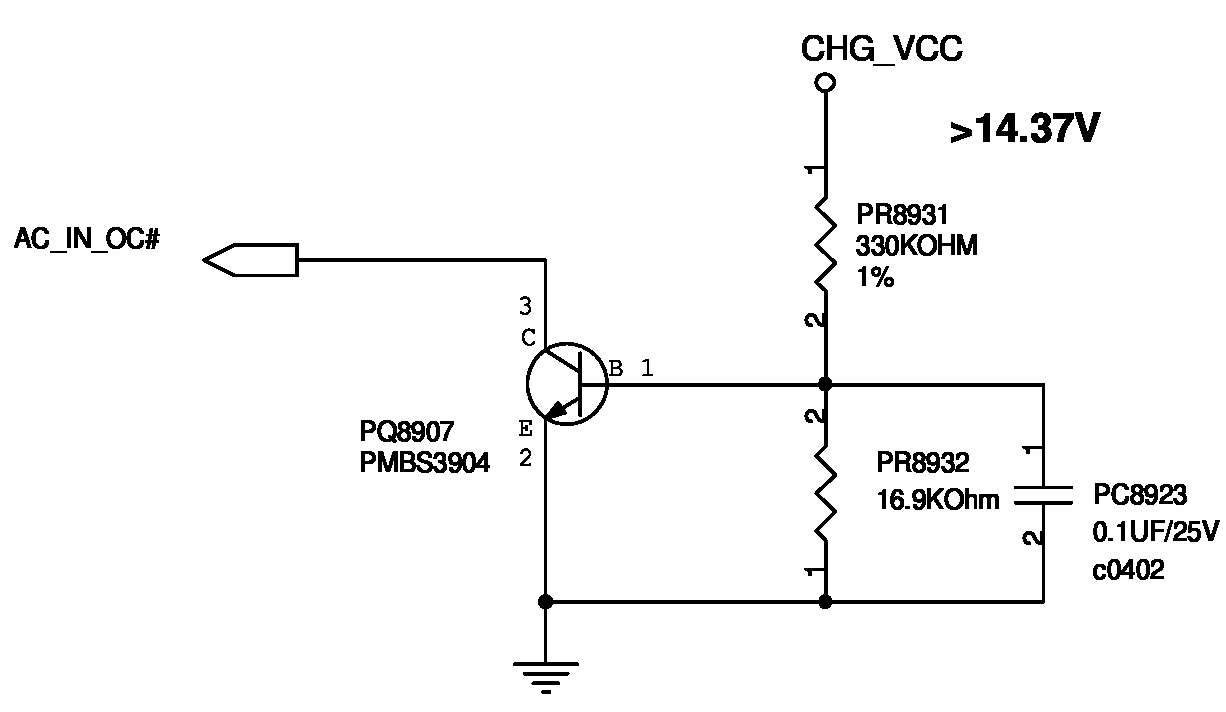

EC从2脚给X3001晶振供电,晶振起振送回频率给EC 128脚。

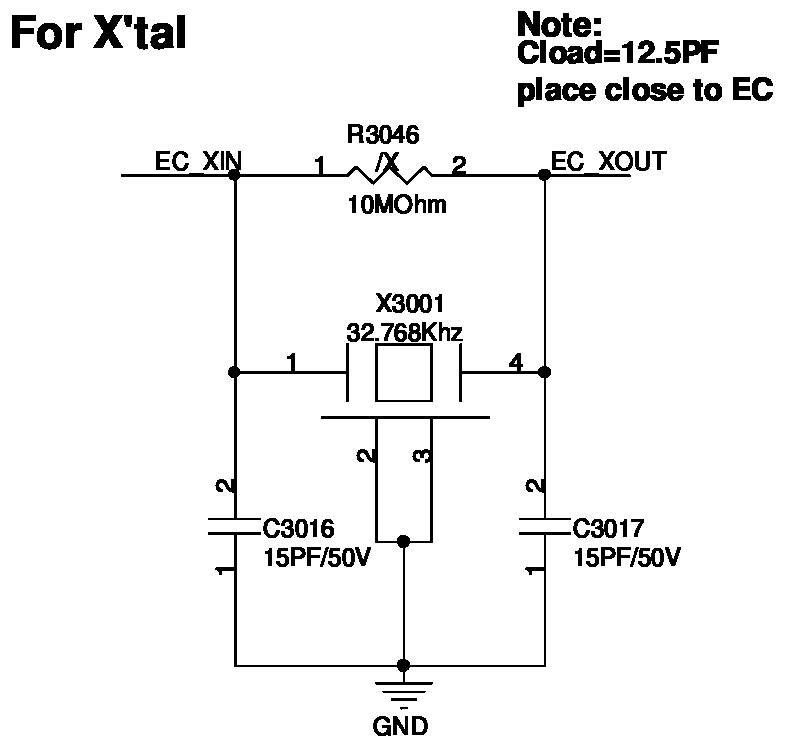

+3VA_EC经过R3023和C3010延时电路给EC提供复位信号。(此信号受控于FORCE_OFF#,后续出现缺电压和温度过高等情况时,会拉低EC的复位实现断电。)

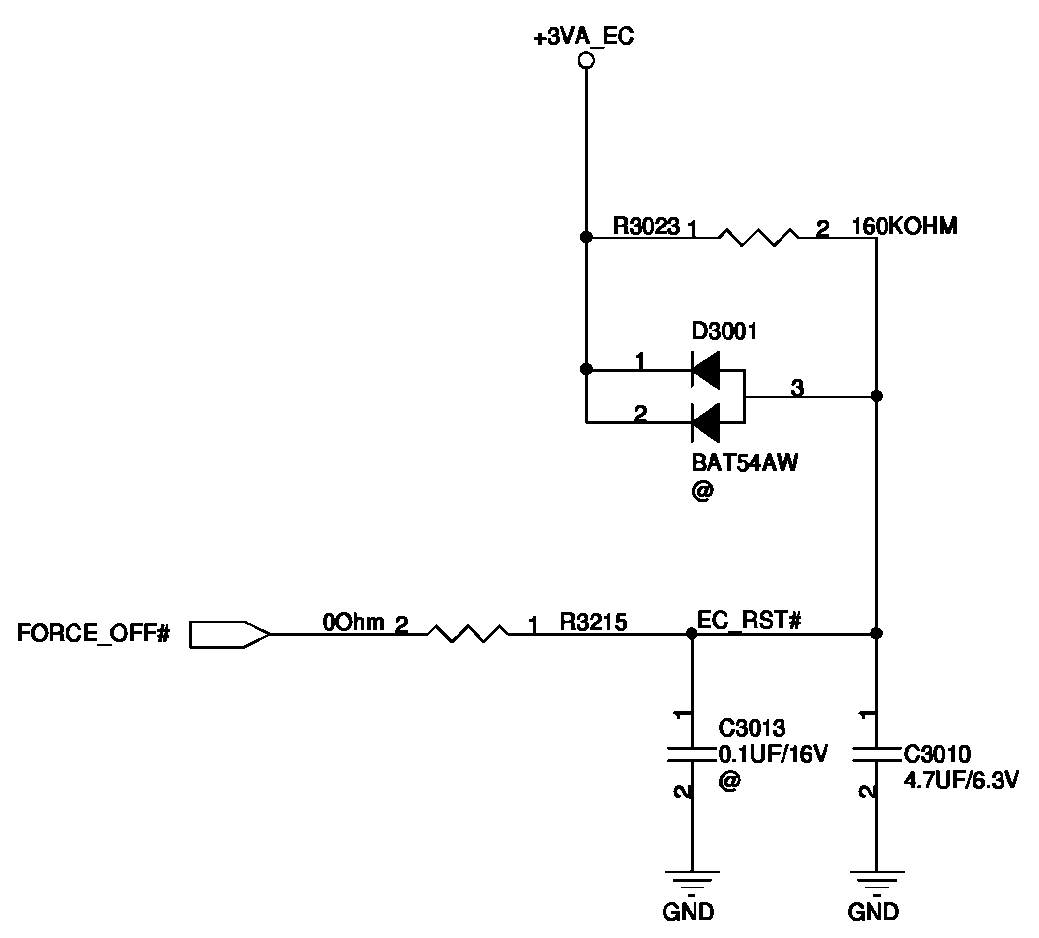

适配器电压大于14.37V后,经过PR8931和PR8932分压能够使PQ8907导通,拉低AC_IN_OC#,送给EC作为适配器检测信号。

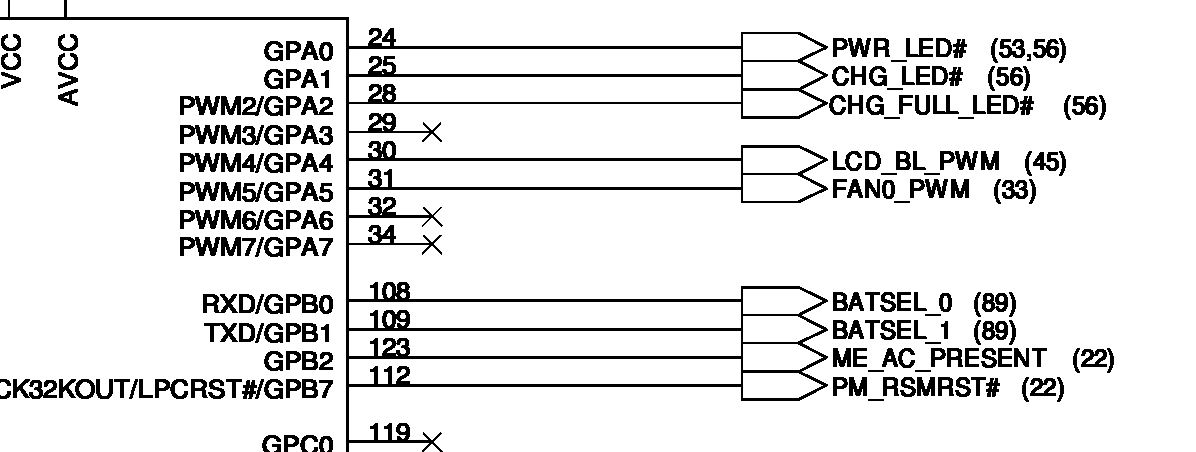

EC待机供电、时钟、复位等条件满足后,开始读取自带的通用程序配置部分与待机有关的脚位,比如VSUSON,适配器检测,电源开关等。

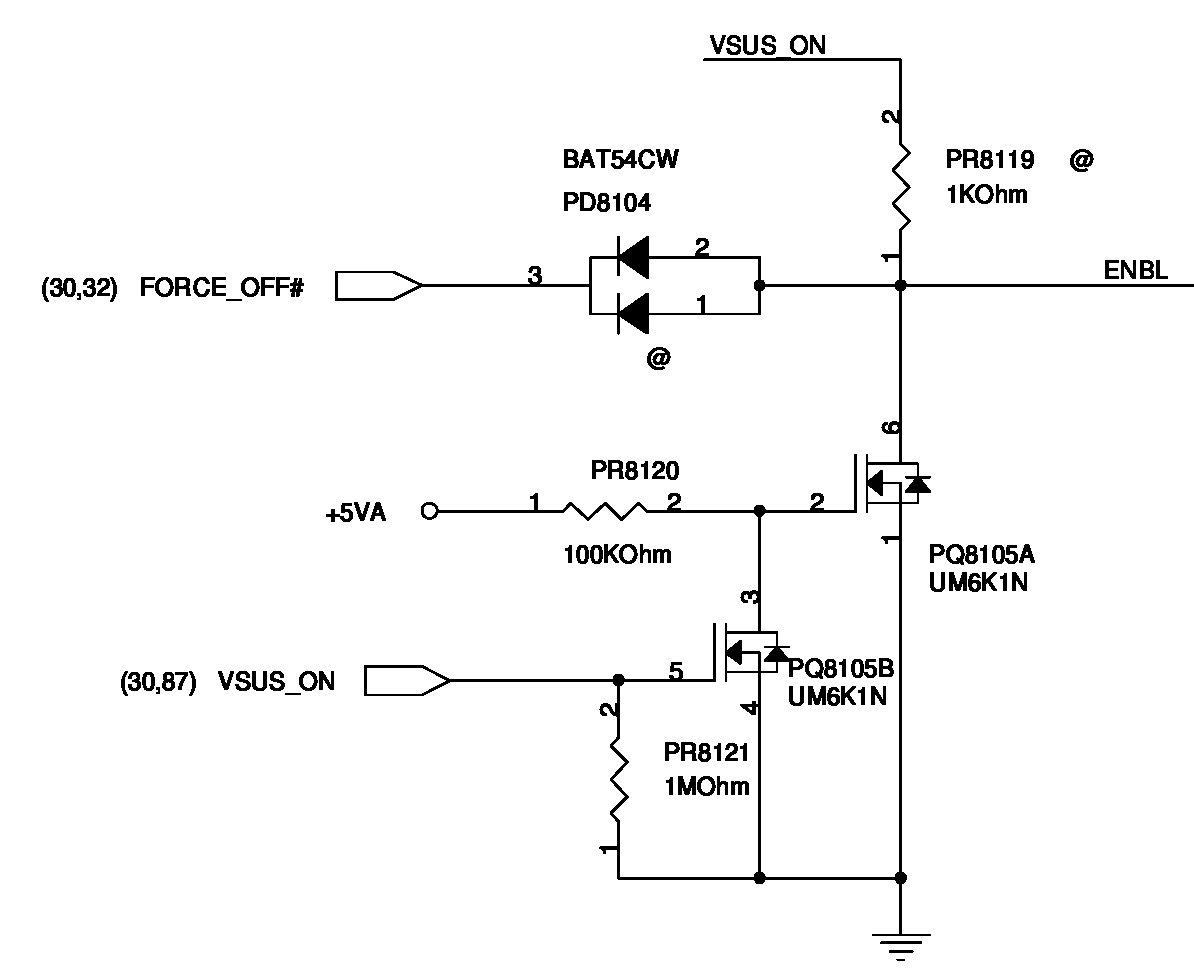

EC识别到适配器插入后(AC_IN_OC#为低),发出VSUS_ON经PQ8105两次开关转换,转换成ENBL信号

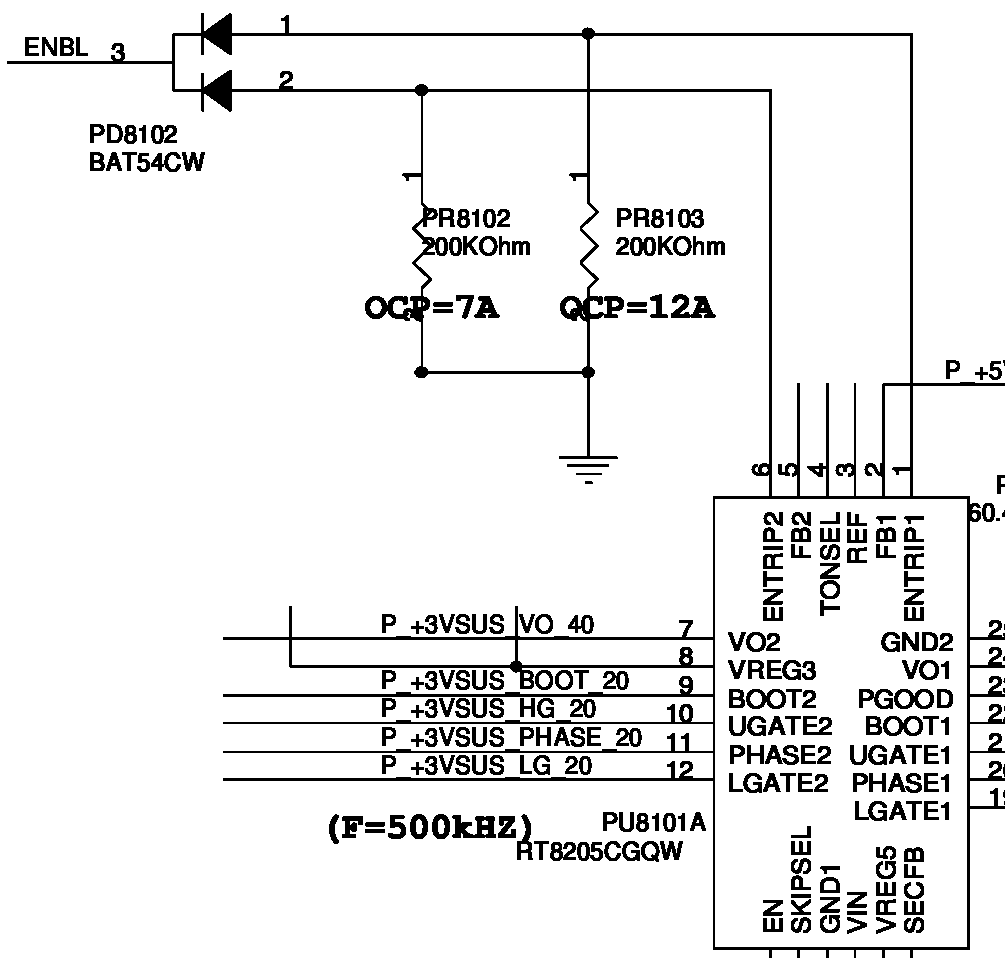

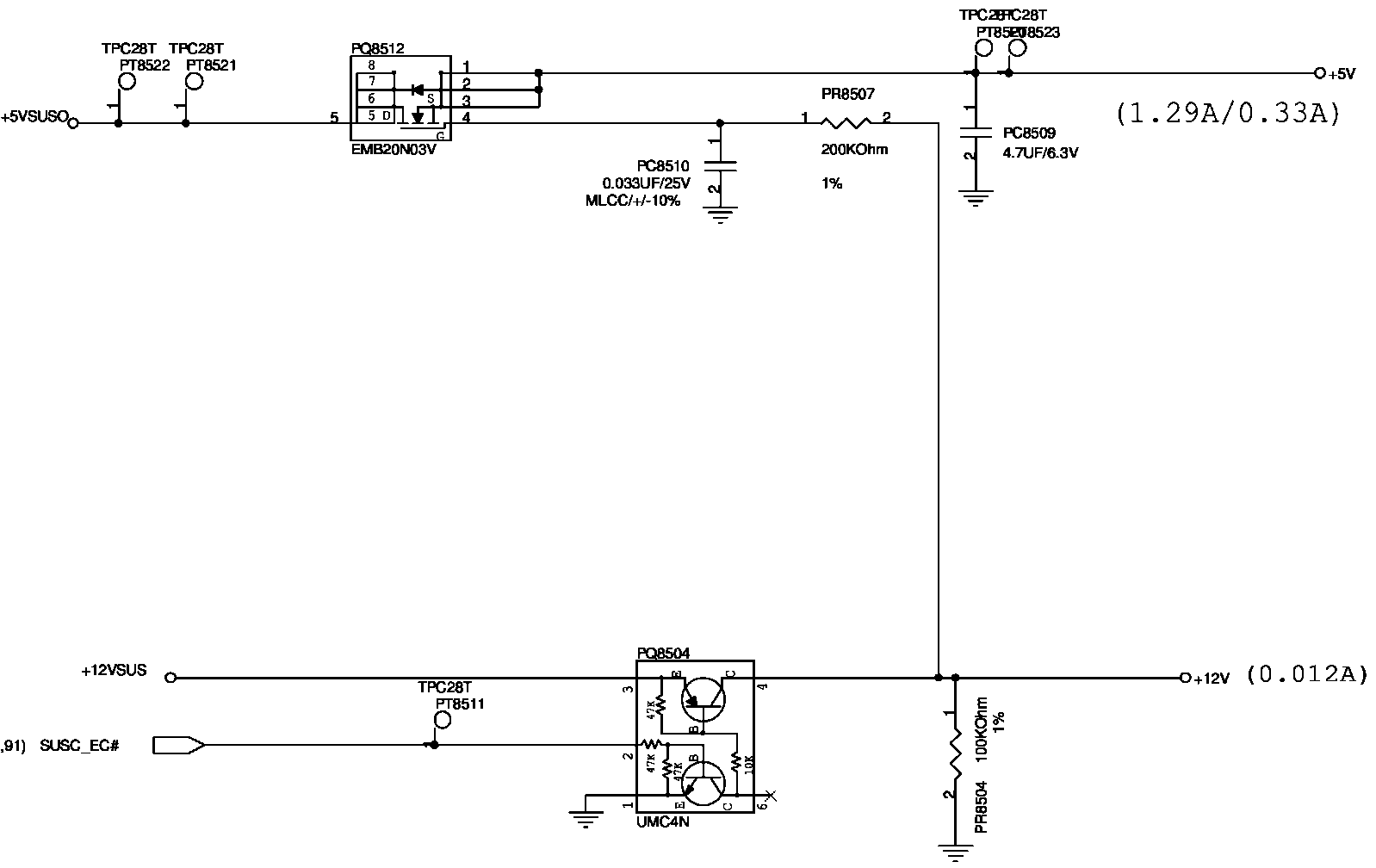

供至待机电源管理芯片RT8205的ENTRIP1、ENTRIP2脚。开启+3VSUS、+5VSUS电压给桥提供待机电压

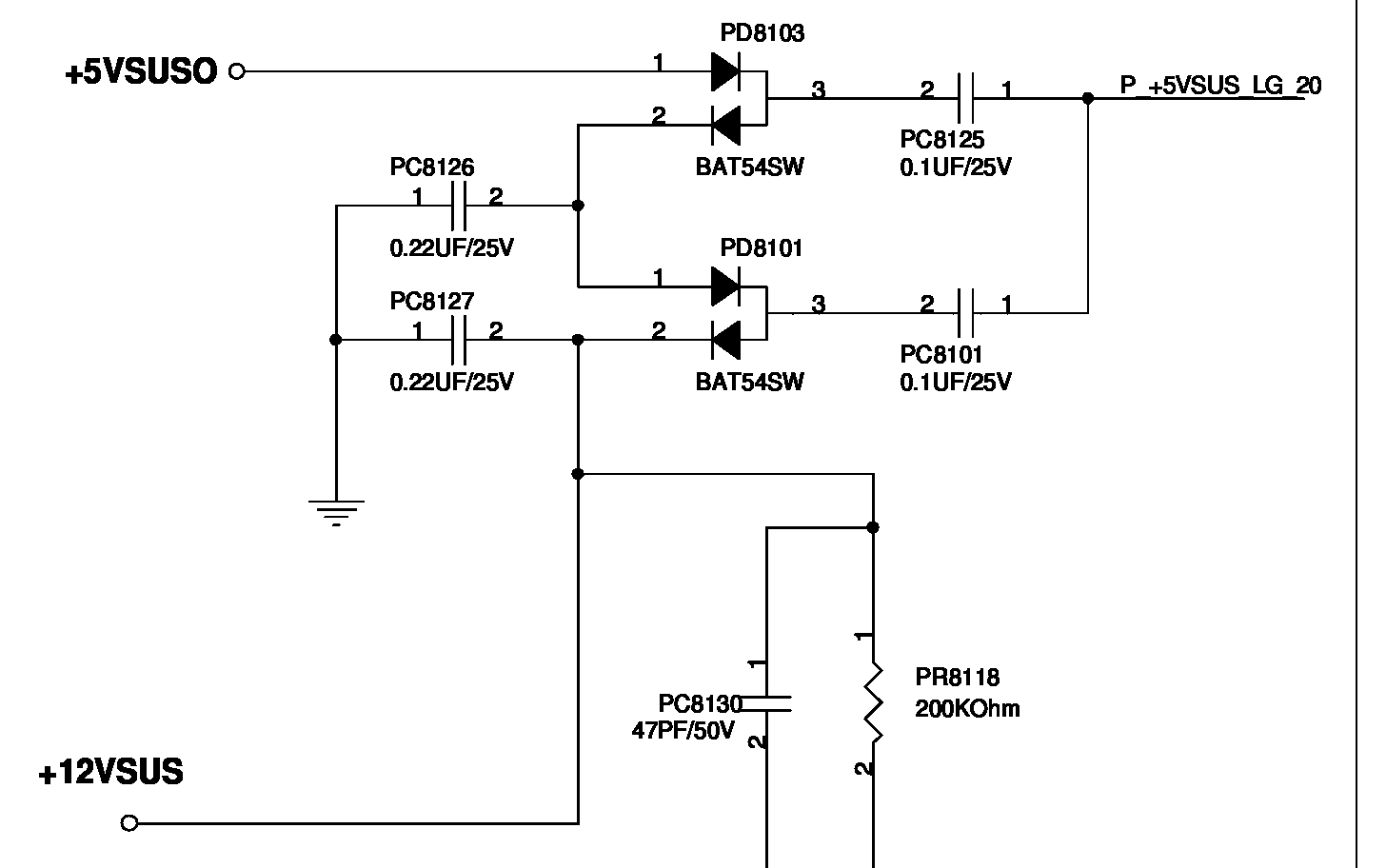

+5VSUS电压与P_+5VSUS_LG_20通过自举升压产生+12VSUS电压。

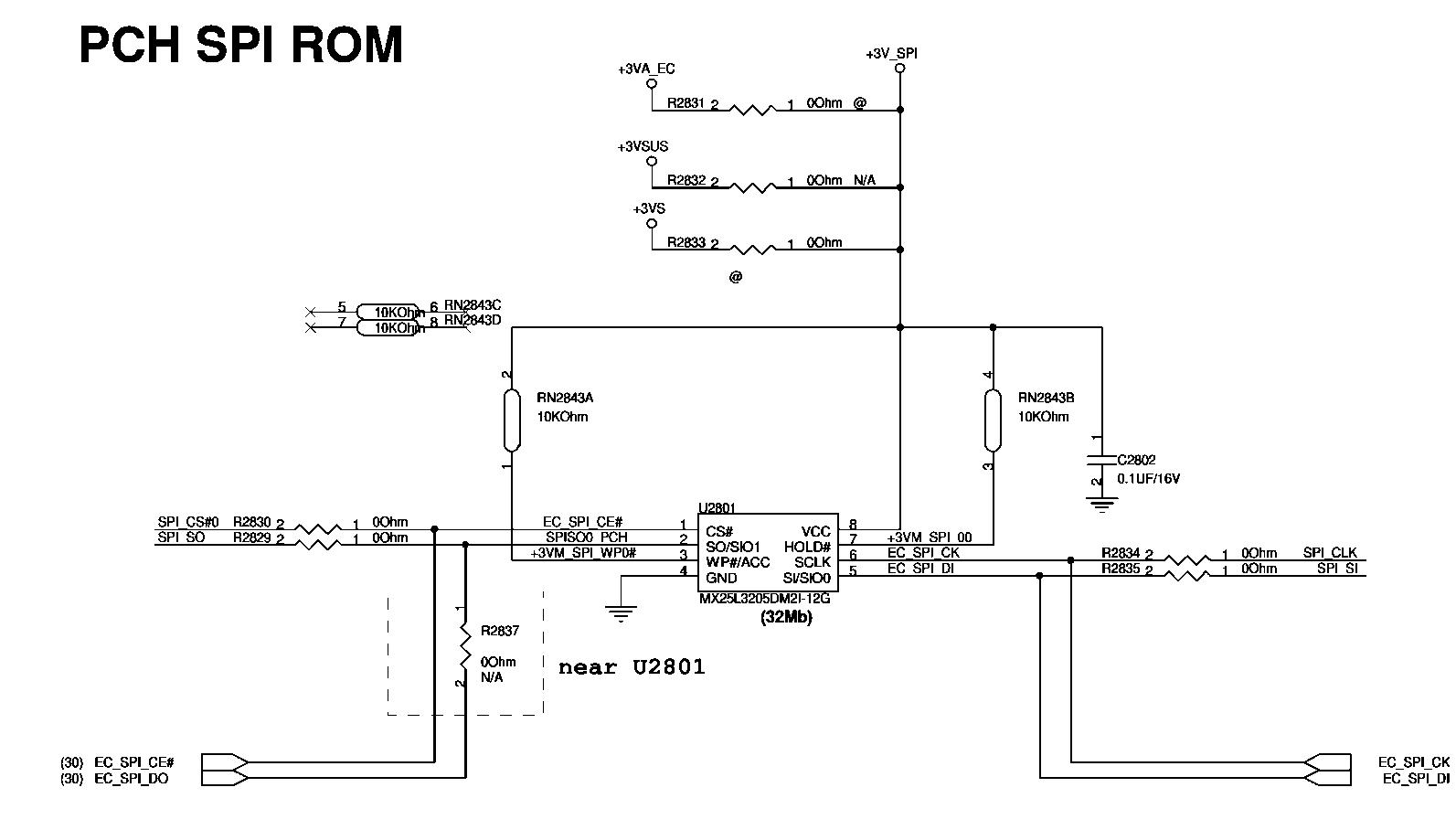

+3VSUS同时送给BIOS

BIOS得到供电后,EC开始读取BIOS程序,配置其他脚位。此次读取,经实测只有瞬间波形,并非持续波形!

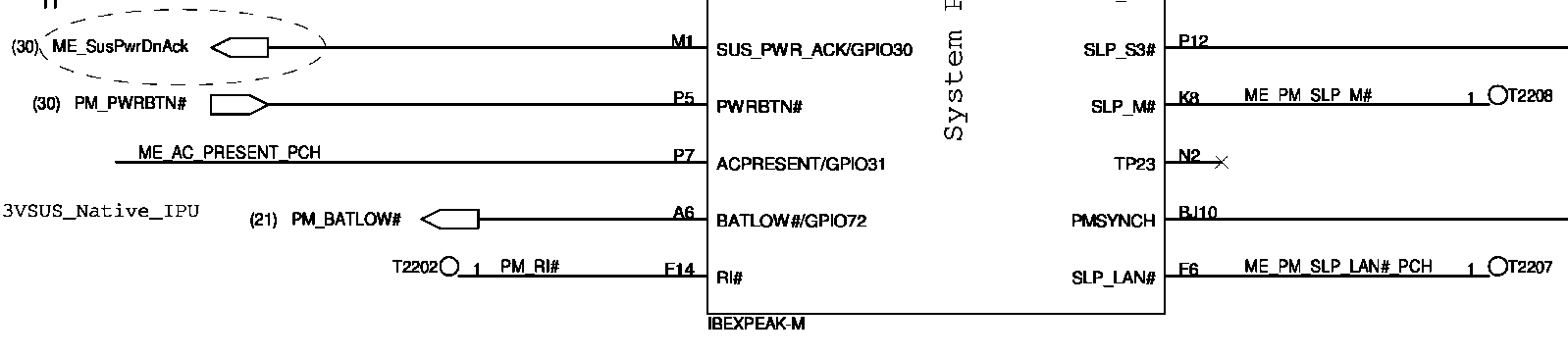

PCH待机电压正常时,PCH内部ME模块输出高电平ME_SusPwrDnAck信号,发至EC。

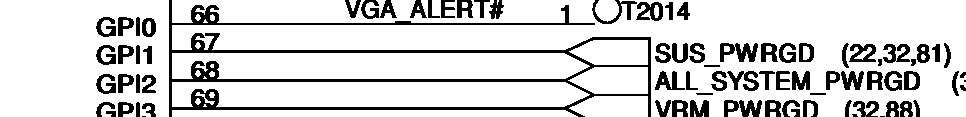

RT8205在待机电压稳定后,输出SUS_PWRGD信号

SUS_PWRGD送至EC,通知EC此时待机电压正常。

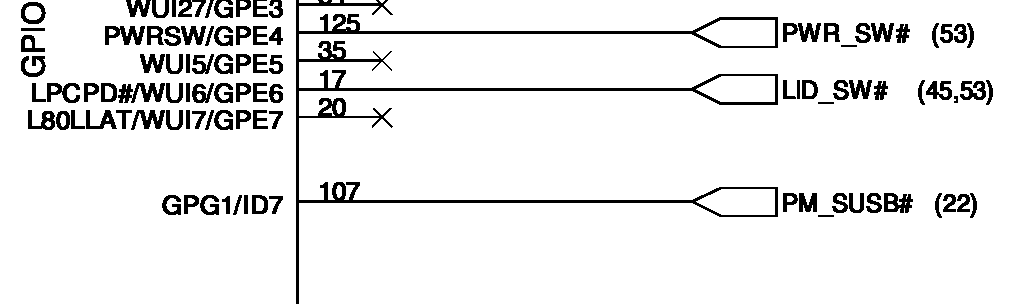

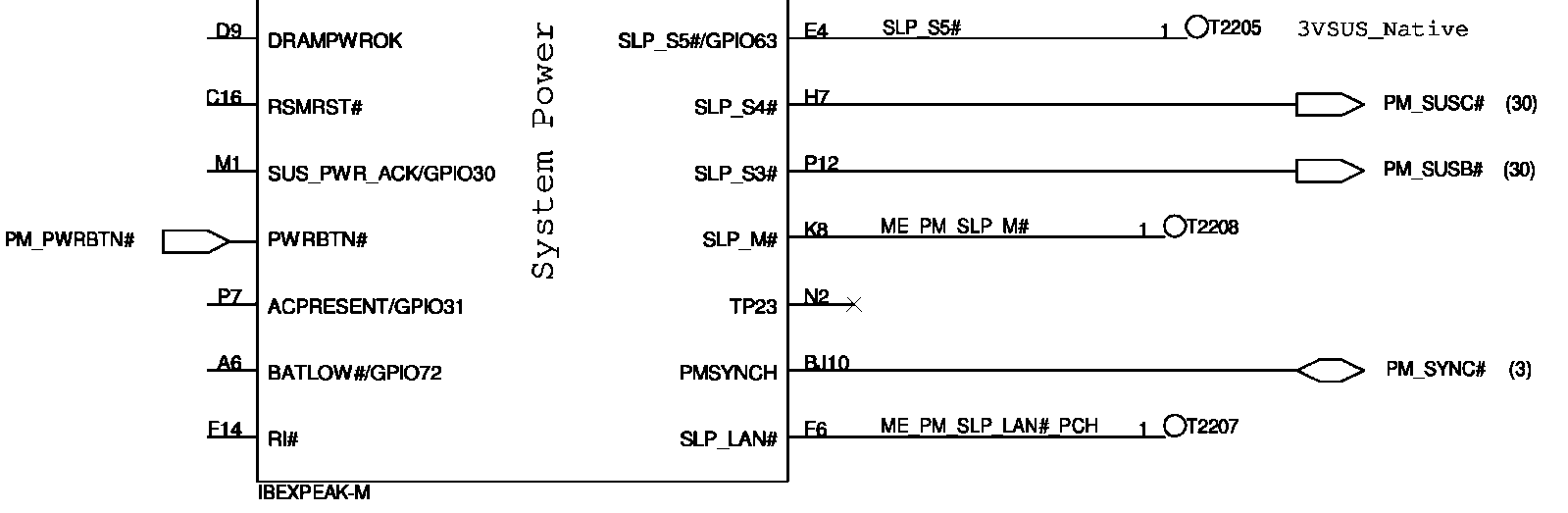

EC发出PM_RSMRST#通知桥待机电压电源好。

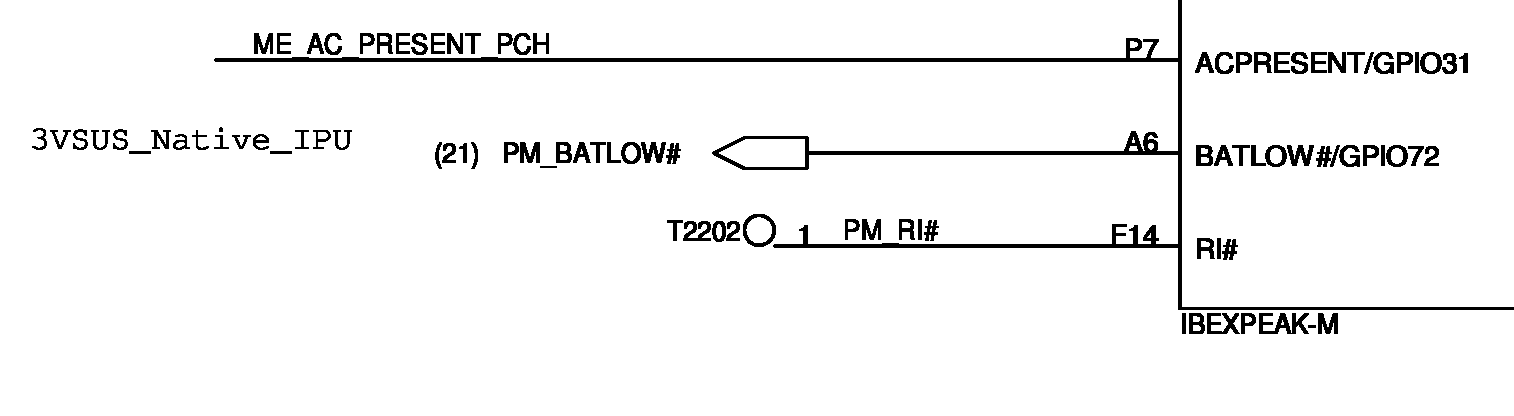

EC发出ME_ACPRESENT_PCH信号送给PCH,通知PCH此时交流适配器插入。

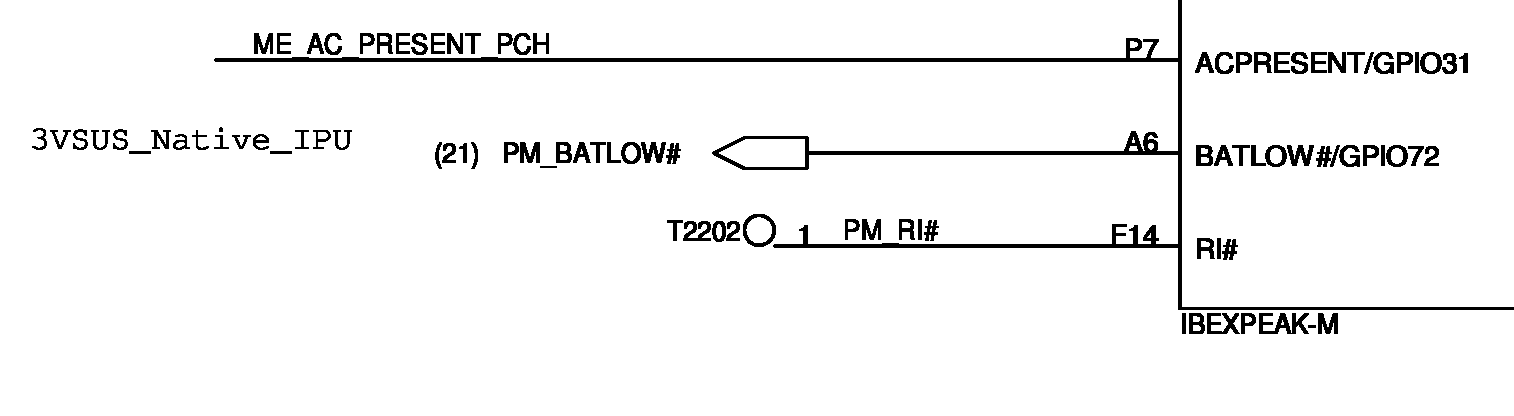

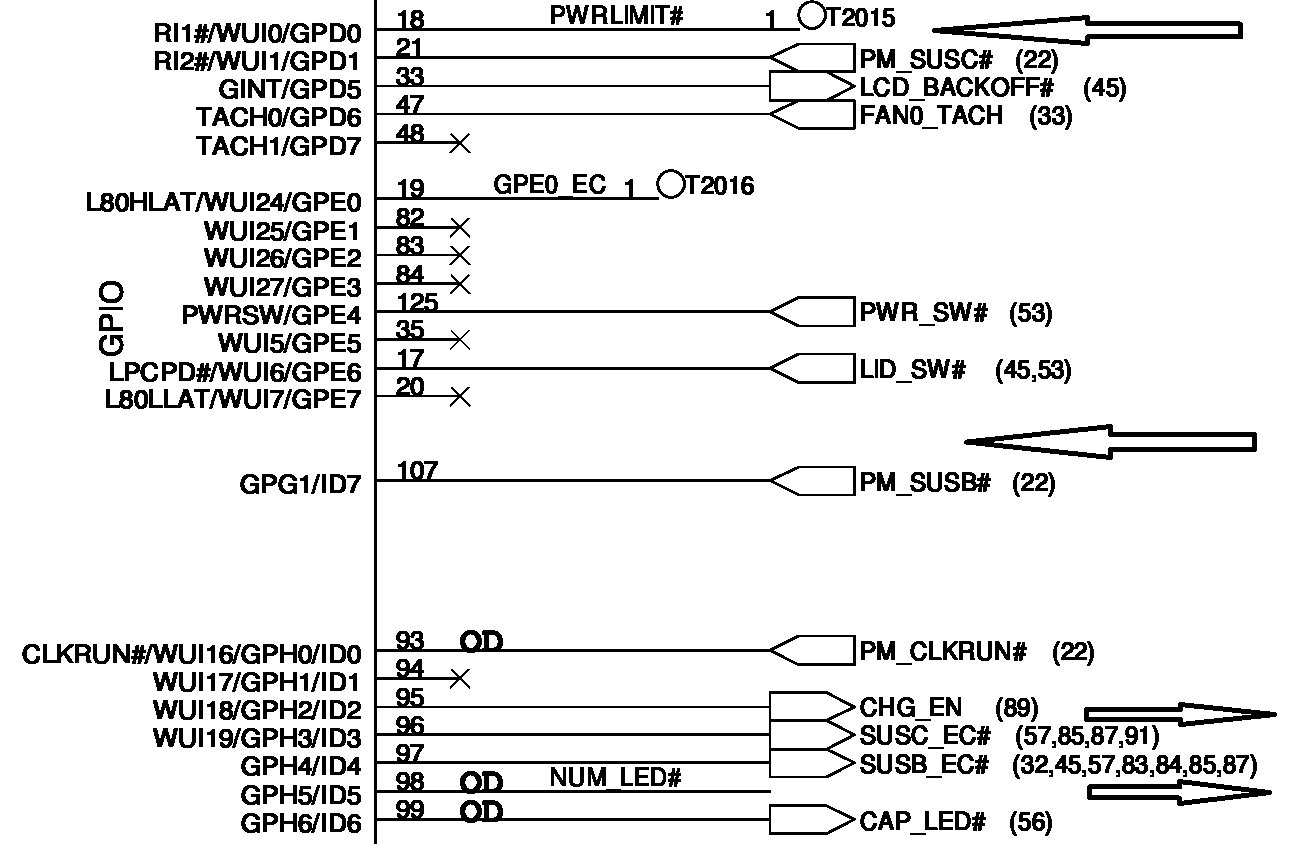

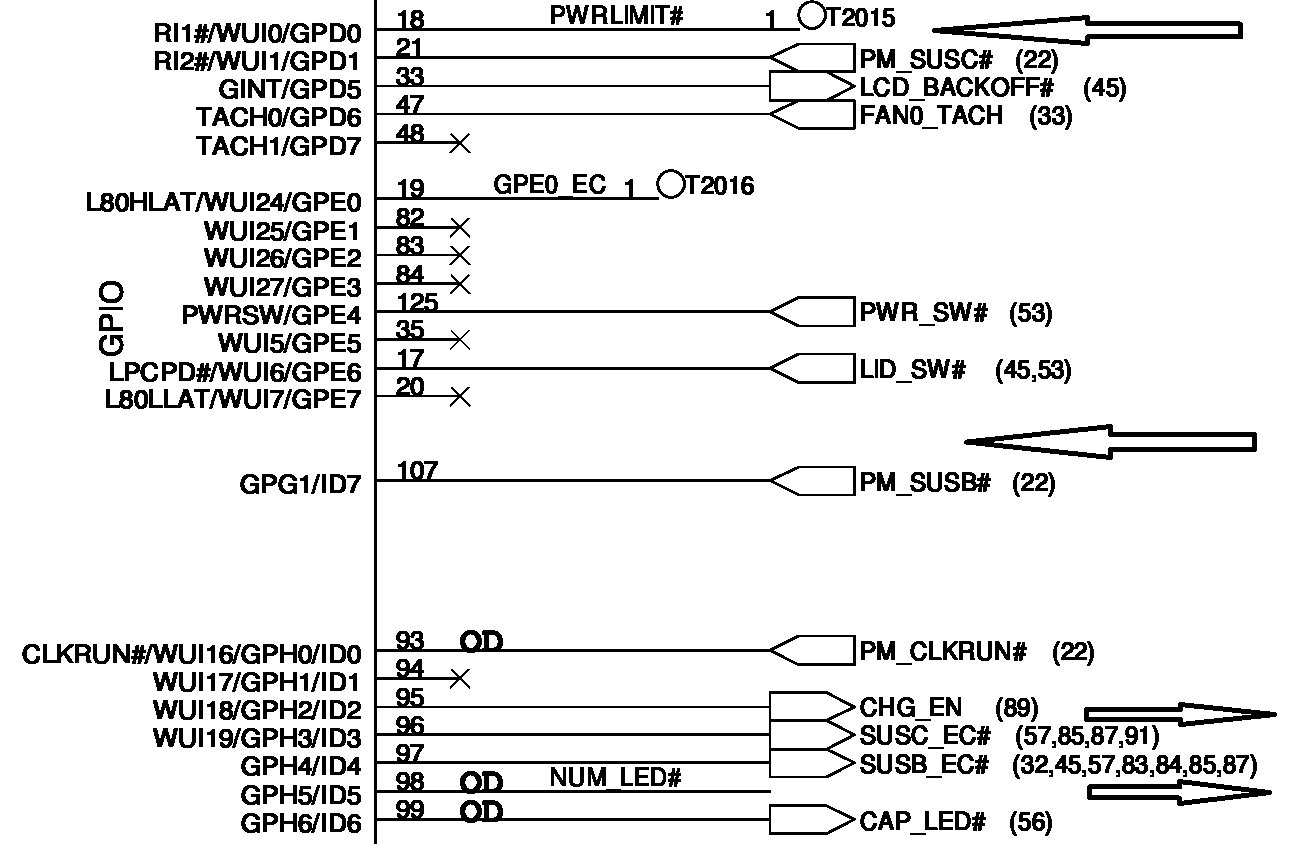

用户按下电源键,产生开机触发信号PWR_SW#至EC 125脚。

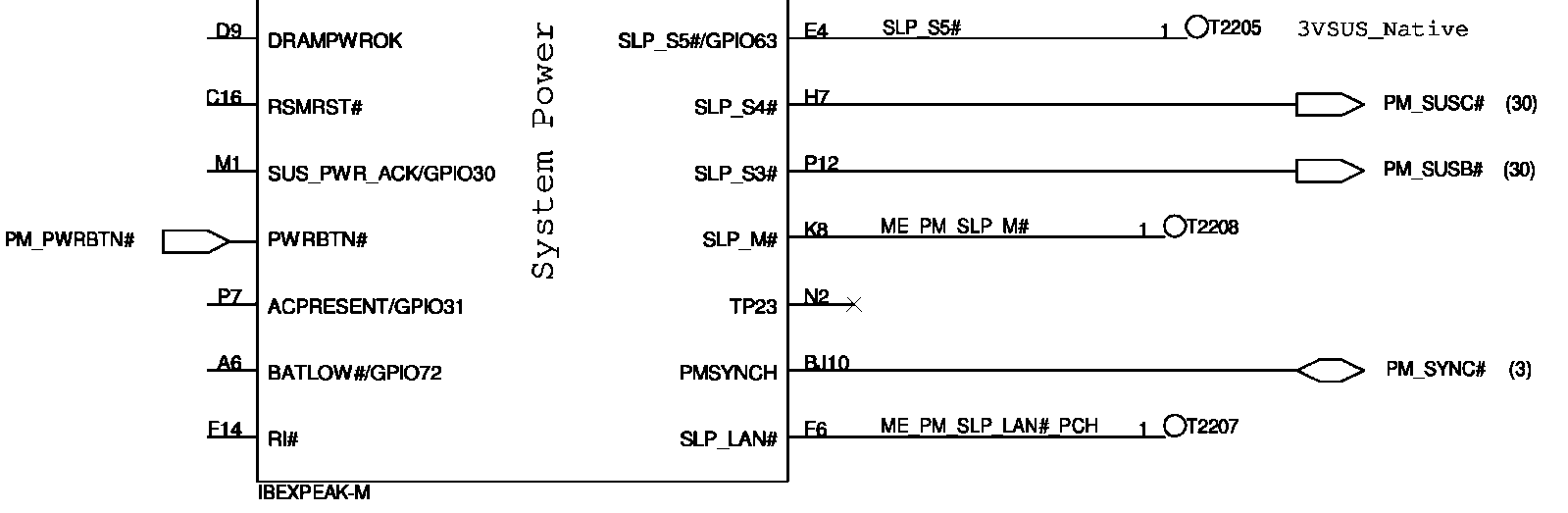

EC发出PM_PWRBTN#至PCH的PWRBTN#,PCH发出SLP_S5#(未采用)、SLP_S4#、SLP_S3#,经更名为PM_SUSC#、PM_SUSB#发至EC。

EC接收到PM_SUSC#、PM_SUSB#后,发出SUSC_EC#、SUSB_EC#。

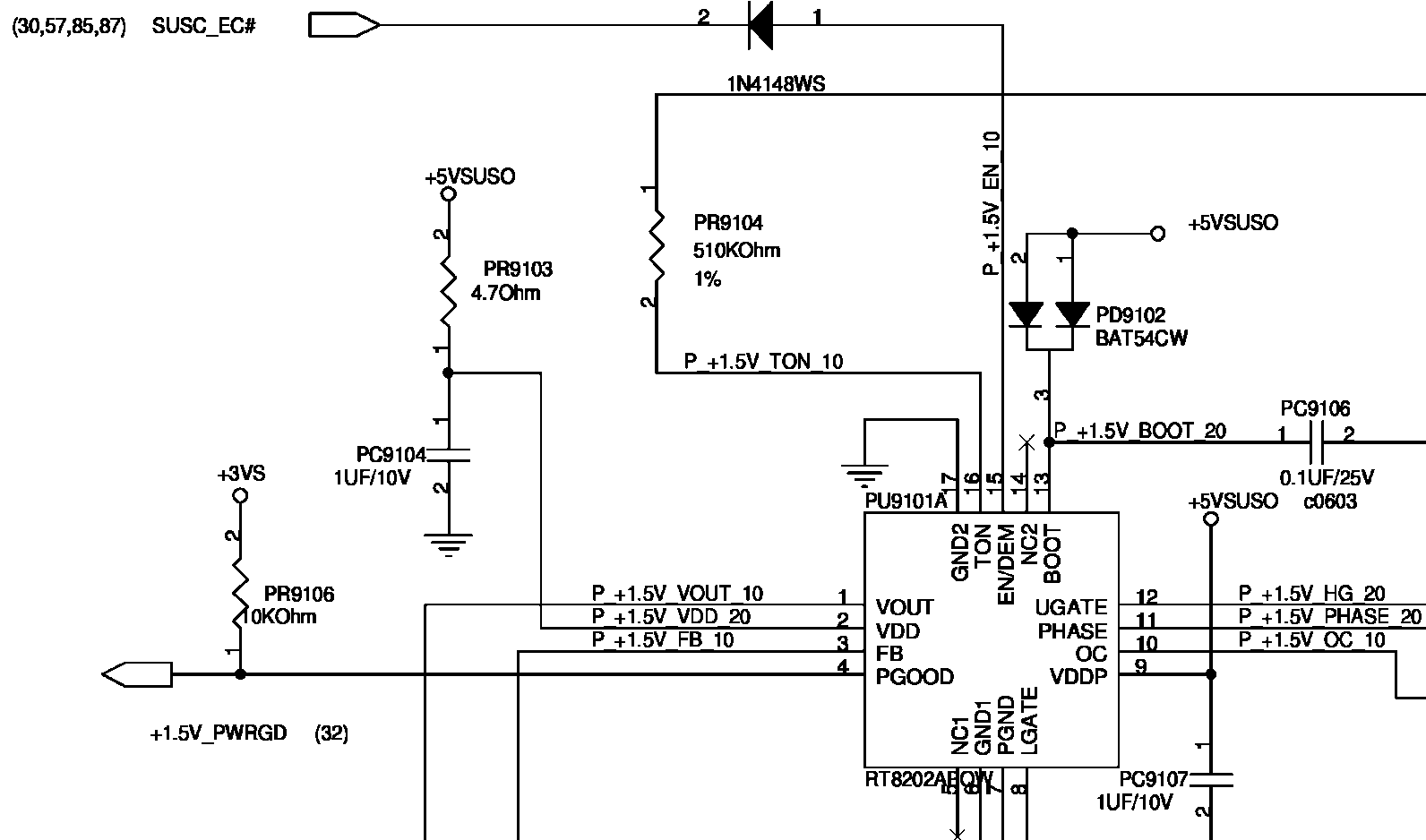

SUSC_EC#至RT8202A(PU9101)开启+1.5VS。

#p#分页标题#e#

#p#分页标题#e#

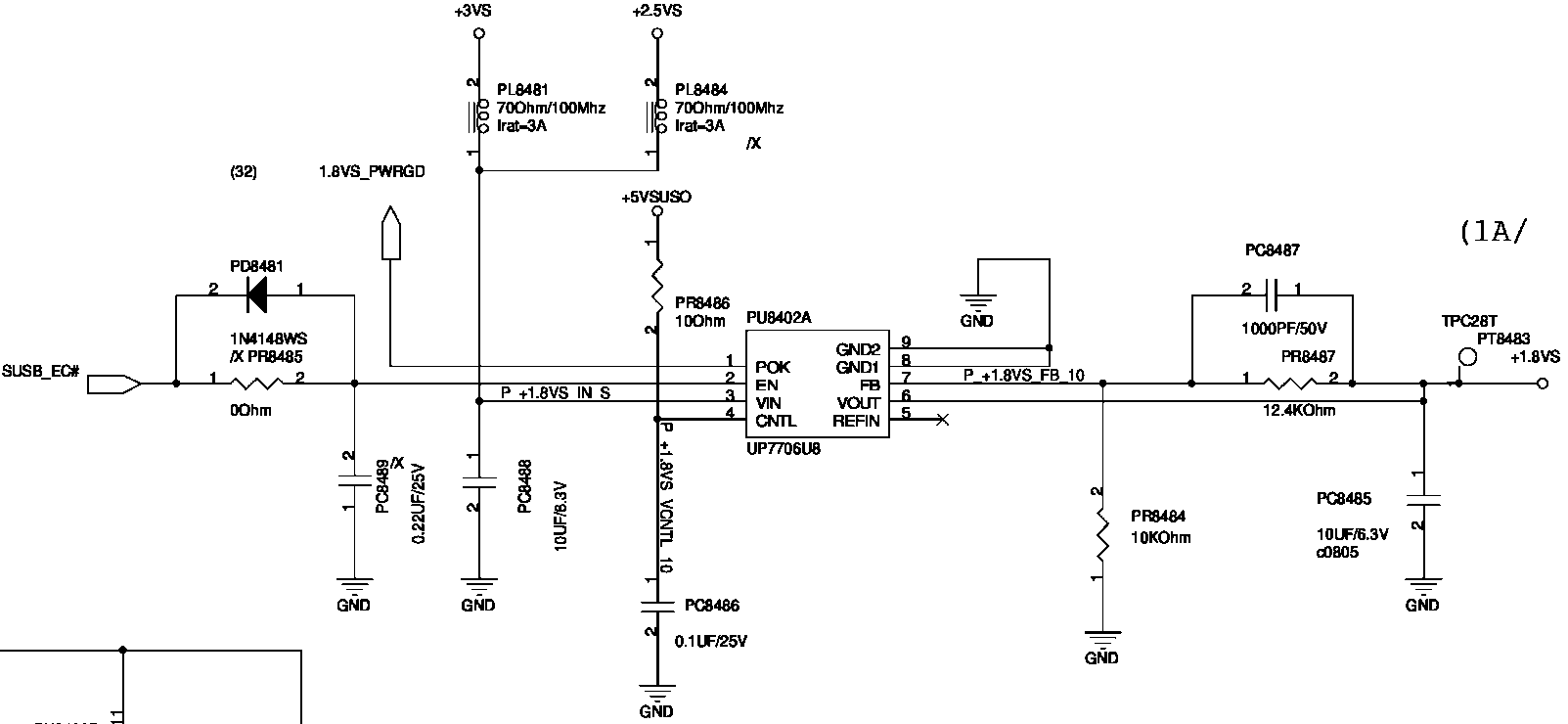

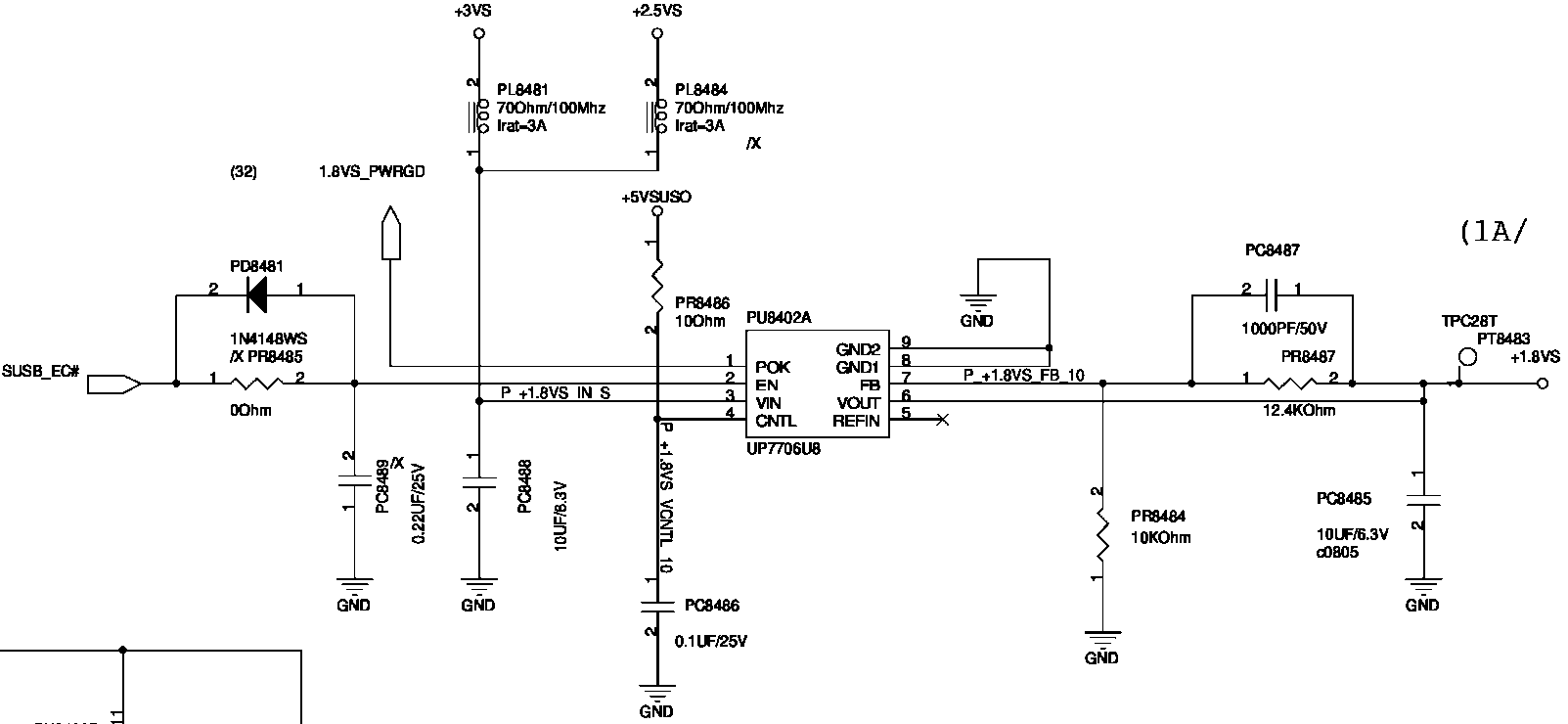

SUSB_EC#至UP7706(PU8402A)开启+1.8VS。然后发出1.8VS_PWRGD

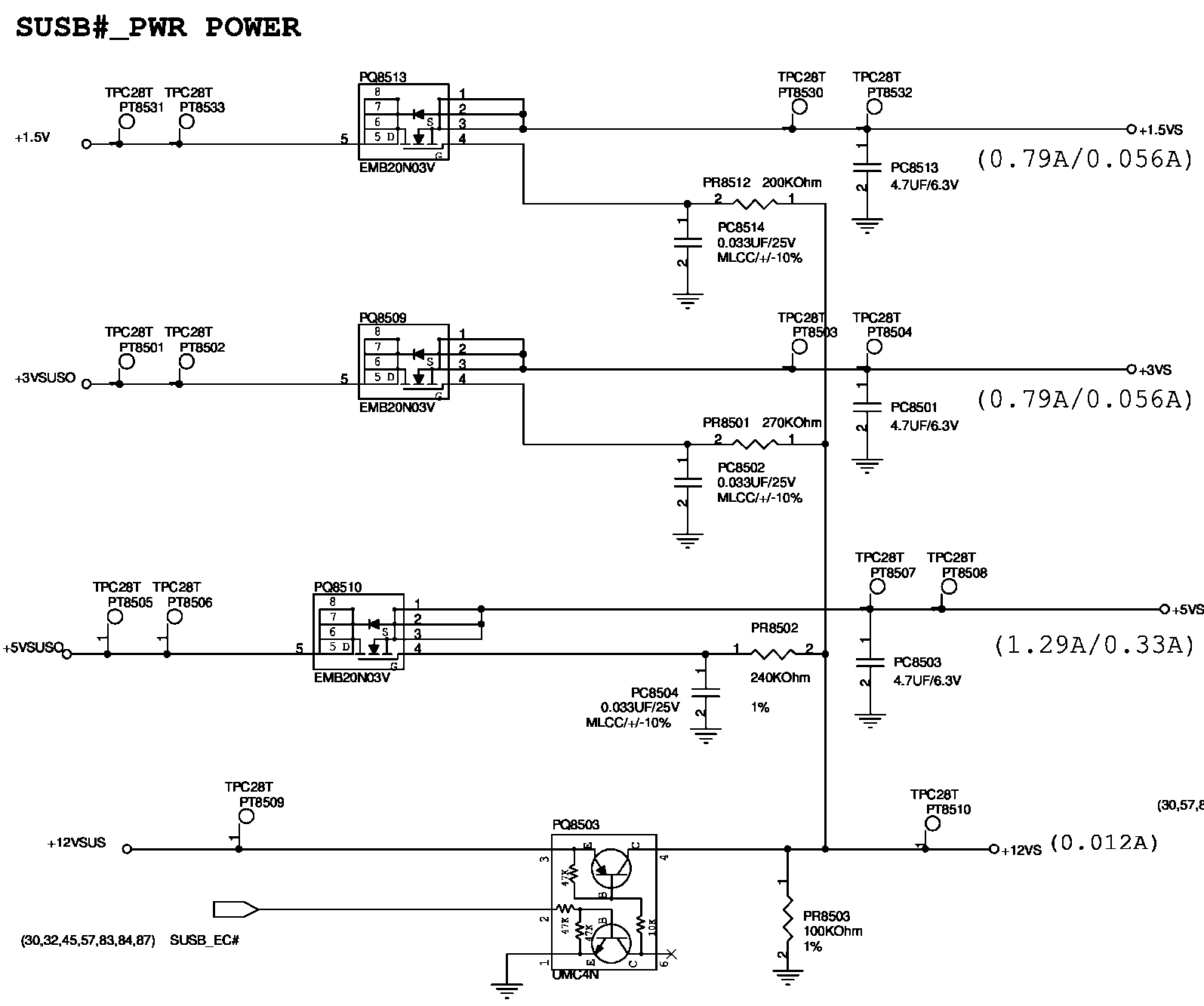

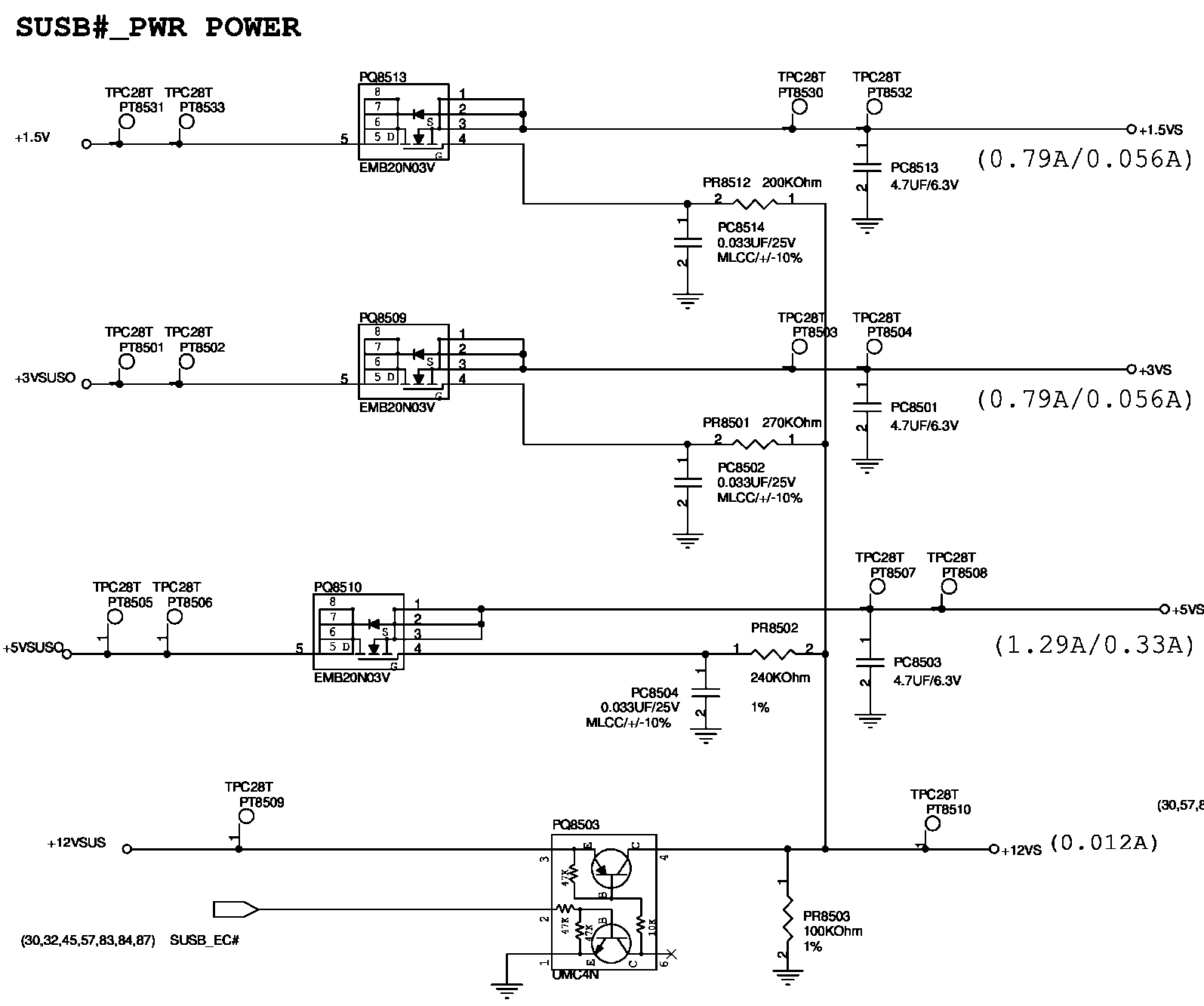

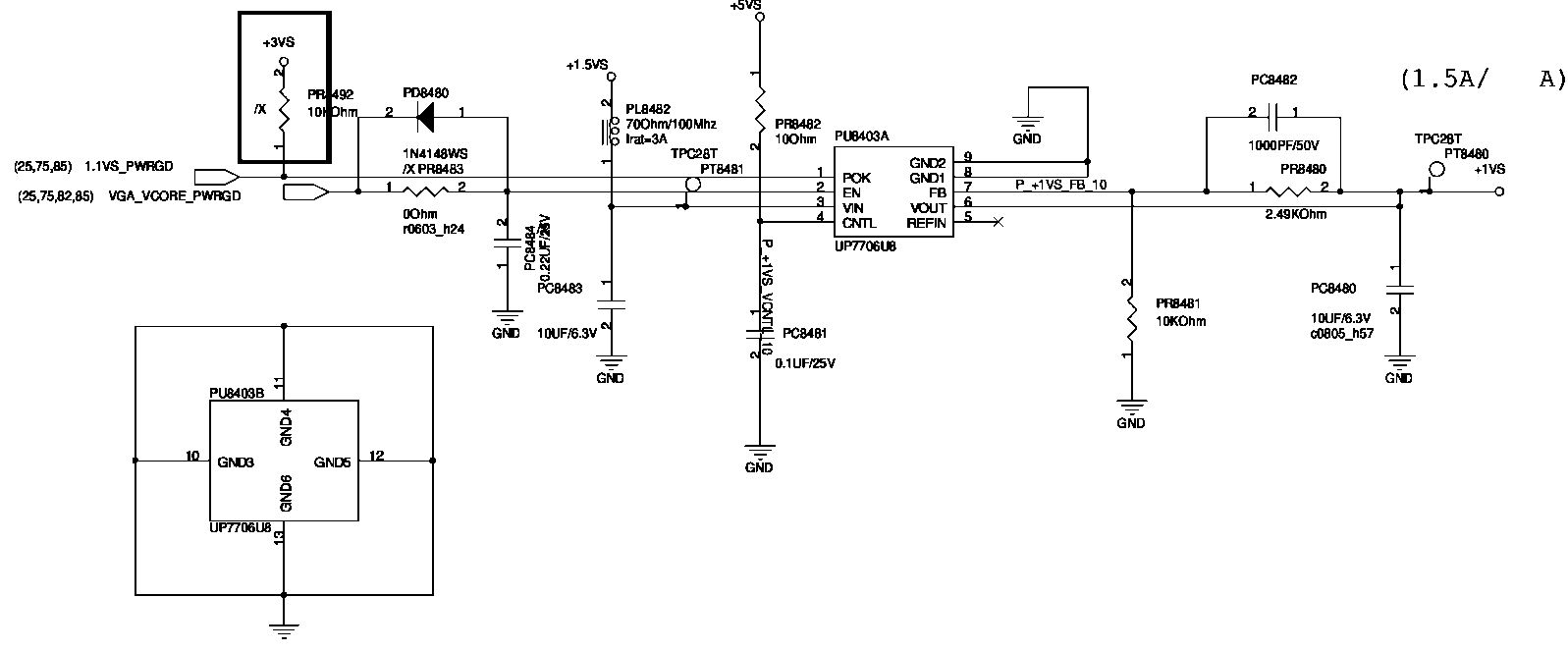

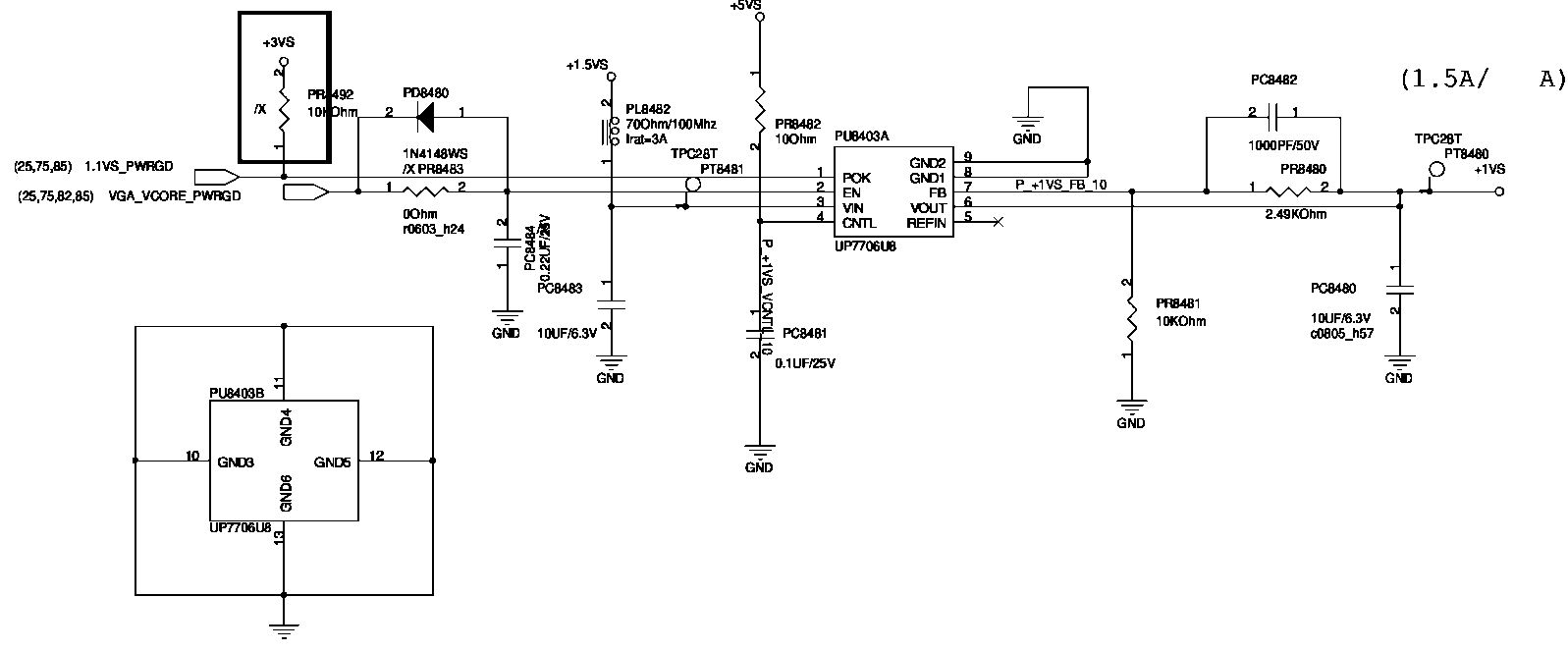

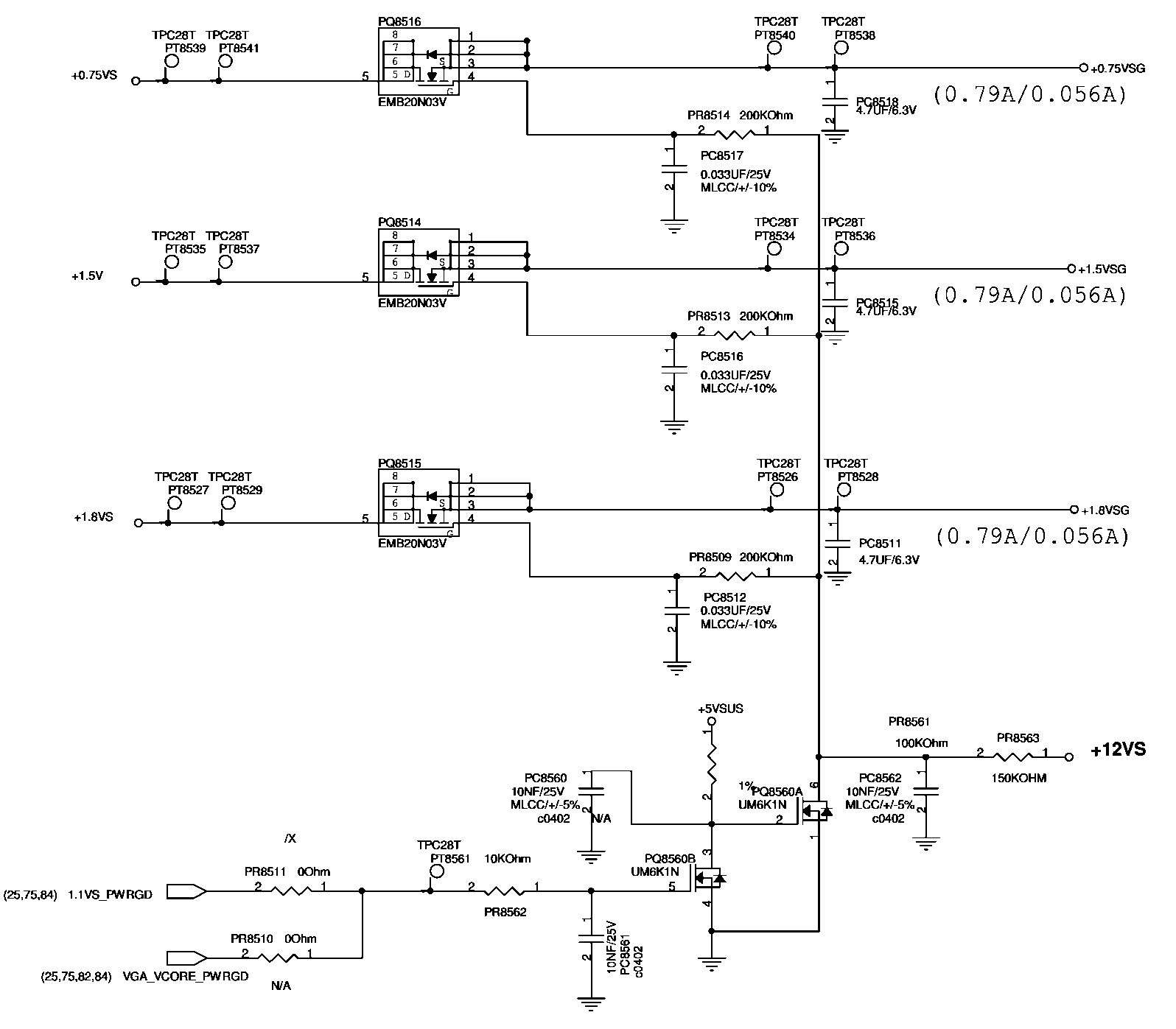

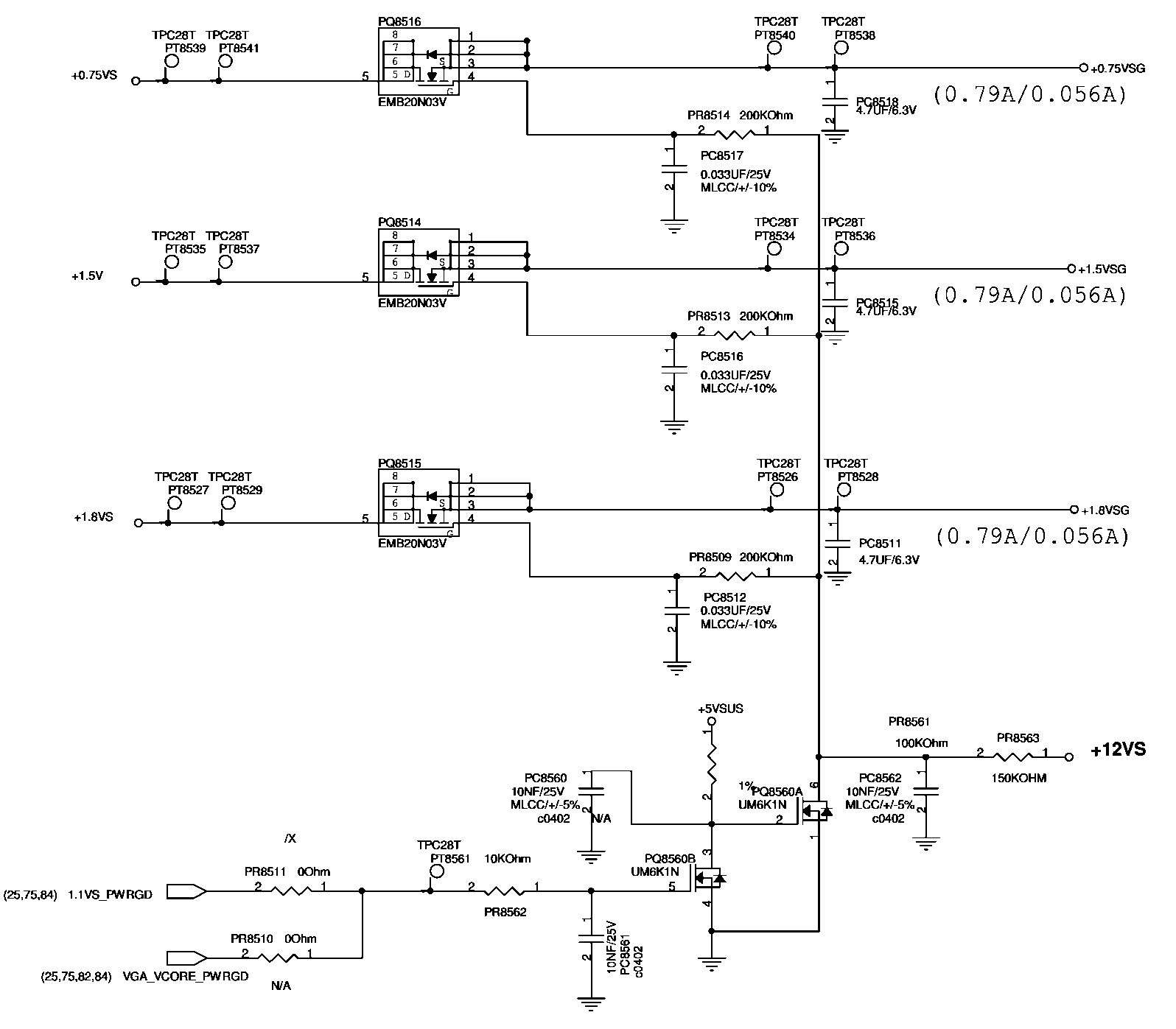

SUSB_EC#至PQ8503开启+12VS,+12VS又分别控制开启+5VS、+3VS、+1.5VS。

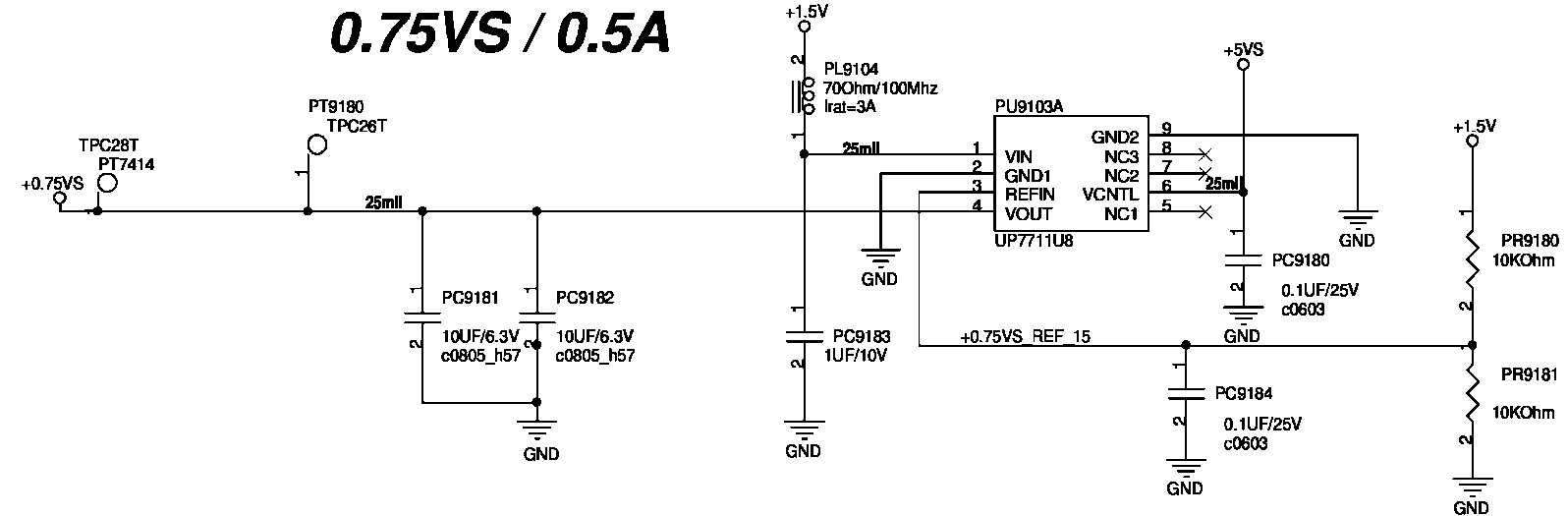

5VS电压送给UP7711(PU9103),控制产生0.75VS。

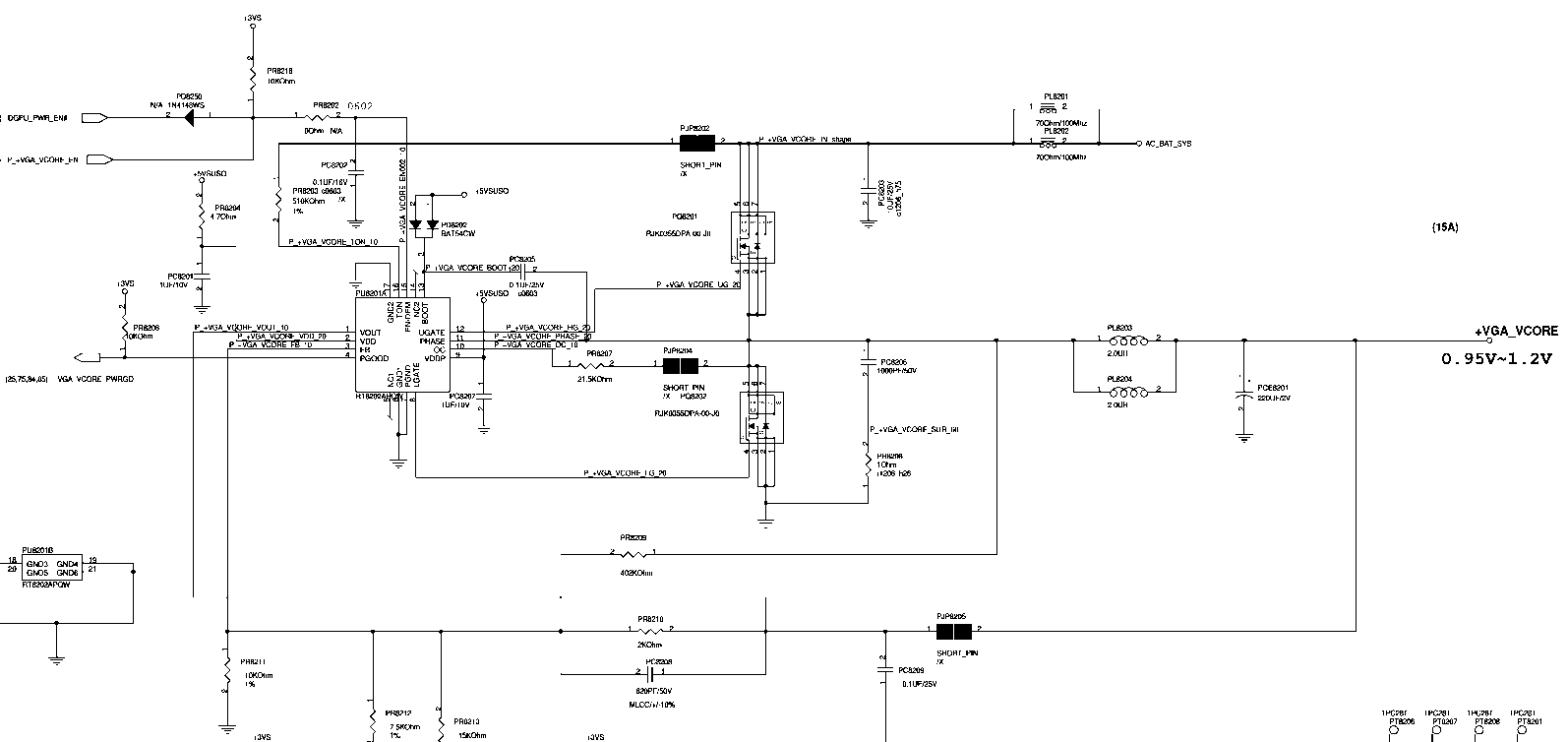

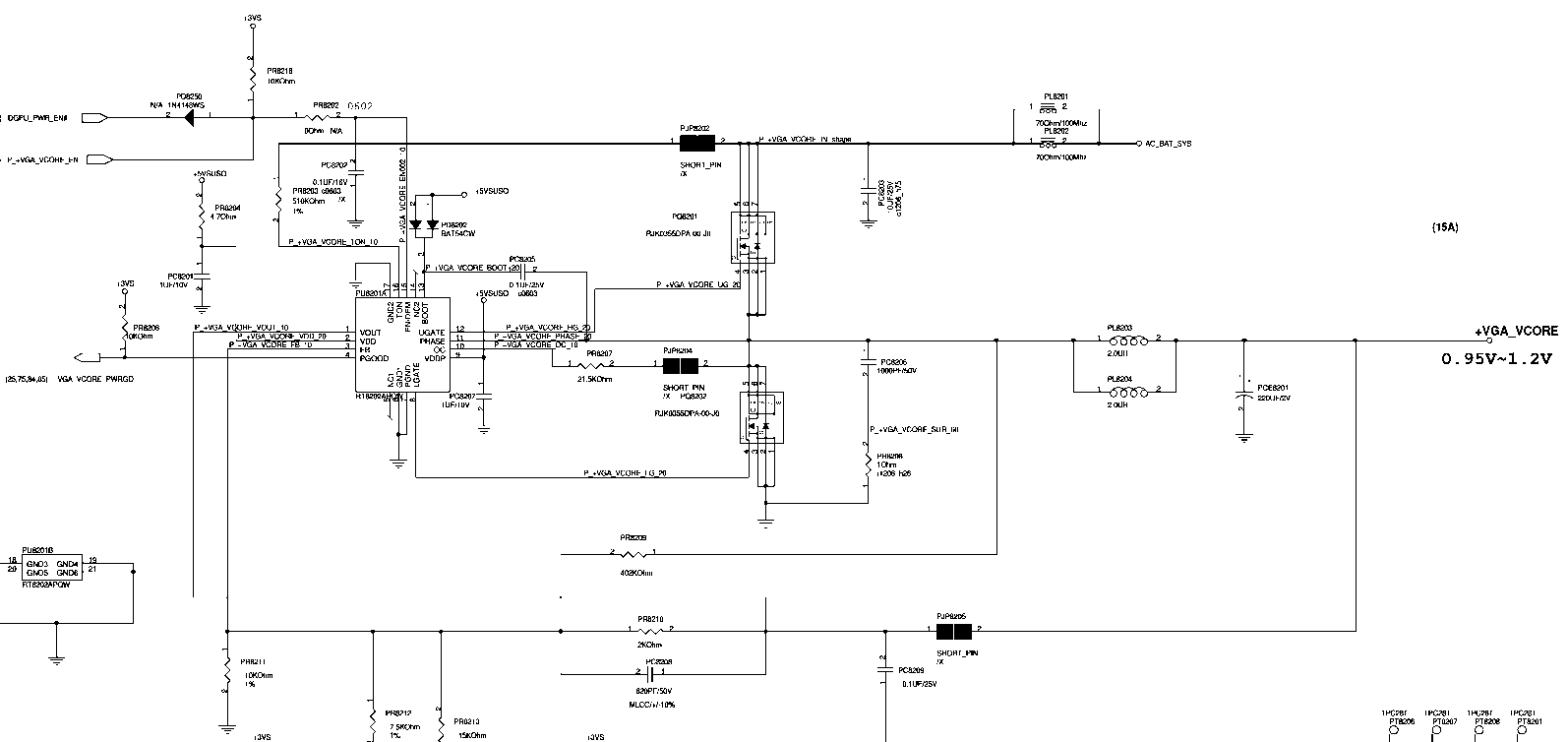

PCH发出DGPU_PWR_EN#至 PU8201产生独显核心供电

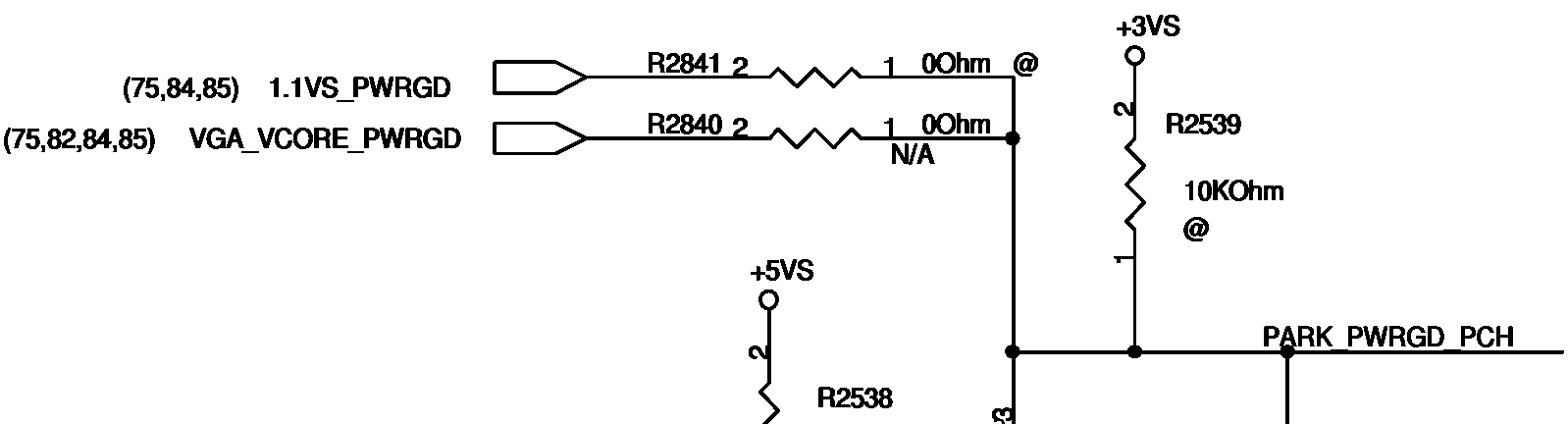

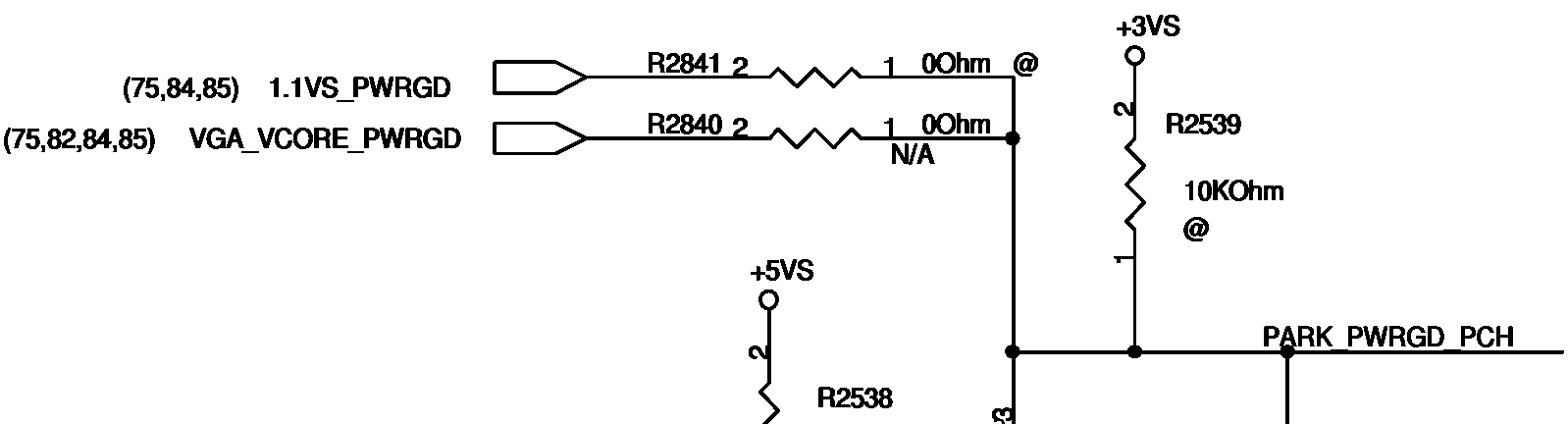

独显核心供电正常后,发出的VGA_VCORE_PWRGD至UP7706(PU8403A)开启+1VS。

VGA_VCORE_PWRGD转换成PARK_PWRGD_PCH送给PCH,通知PCH此时显卡供电已经就绪

VGA_VCORE_PWRGD送至PQ8560,经过转换控制+0.75VSG、+1.5VSG、+1.8VSG

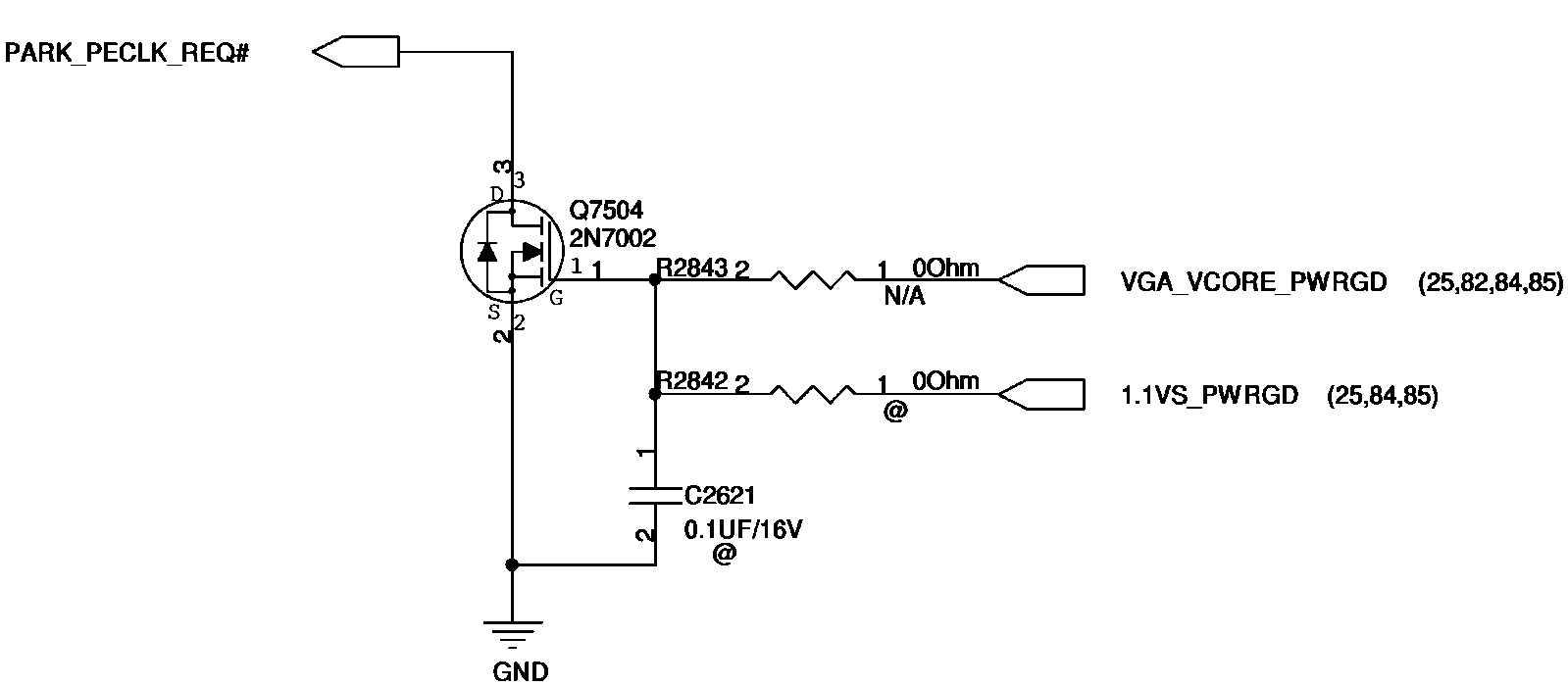

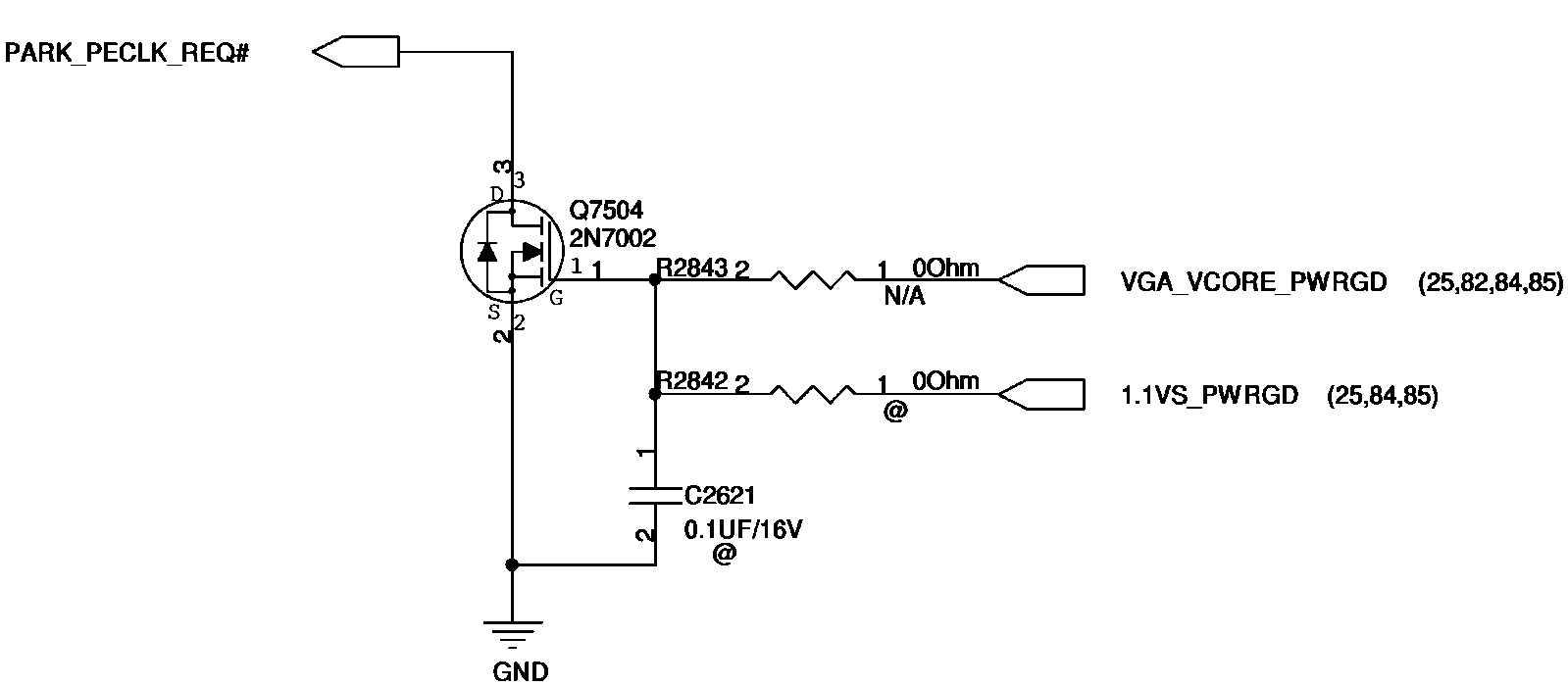

VGA_VCORE_PWRGD还送给Q7504转换出PARK_PECLK_REQ#给PCH,请求发出显卡的100M总线时钟

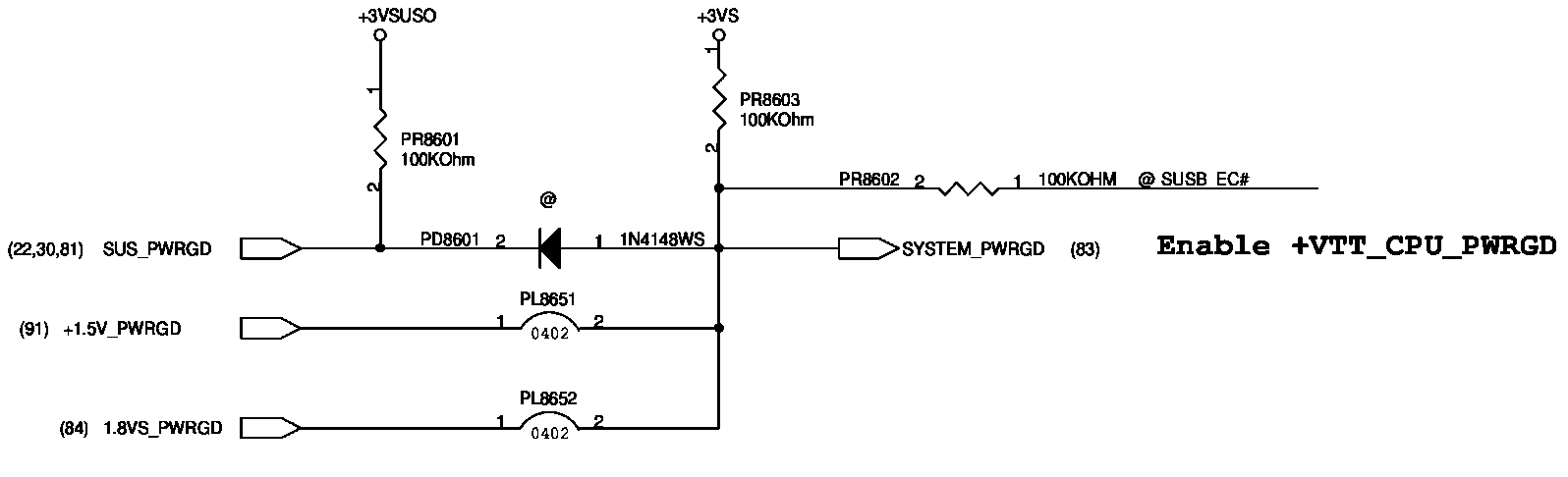

+1.5V_PWRGD与1.8VS_PWRGD相与产生SYSTEM_PWRGD。

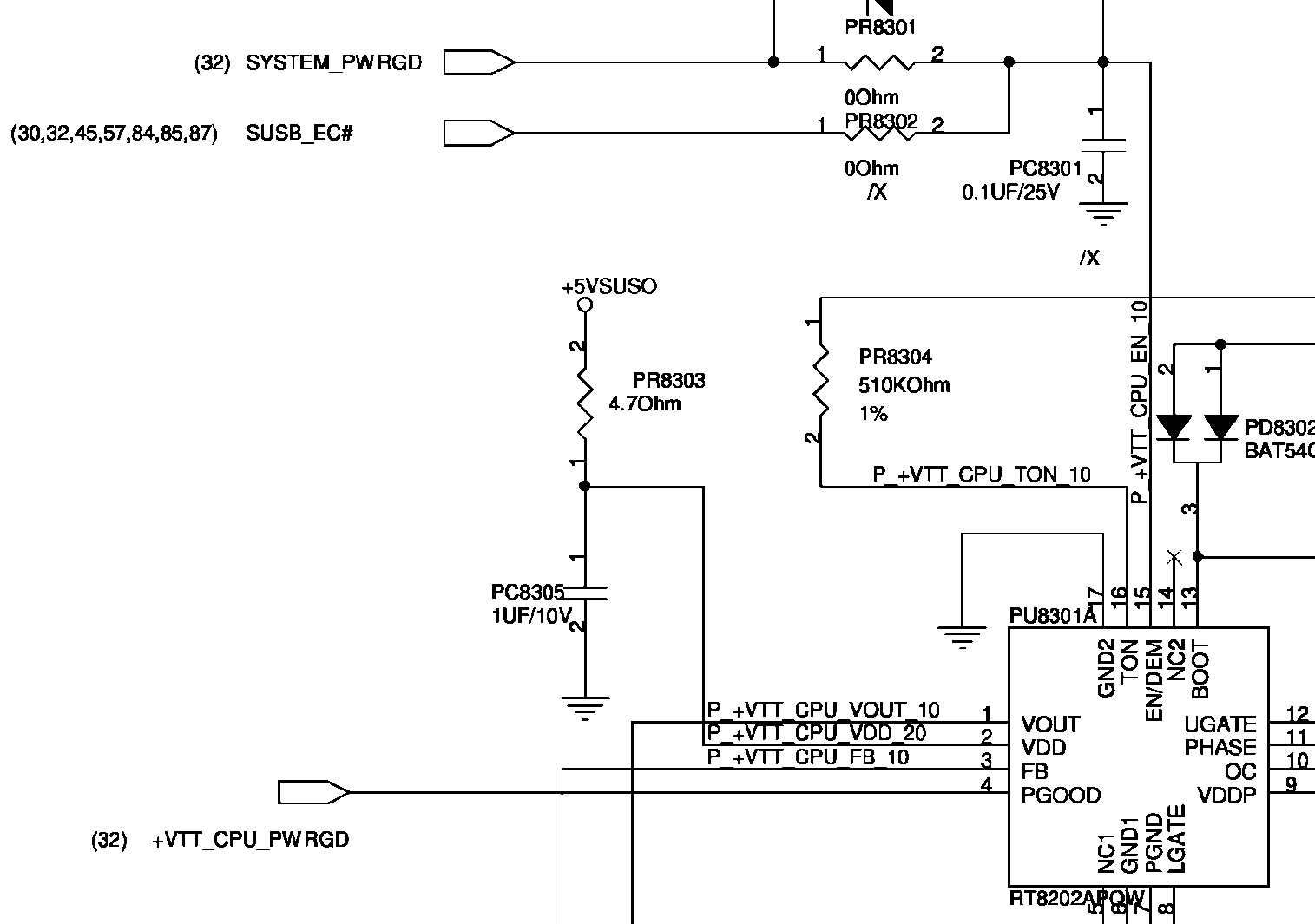

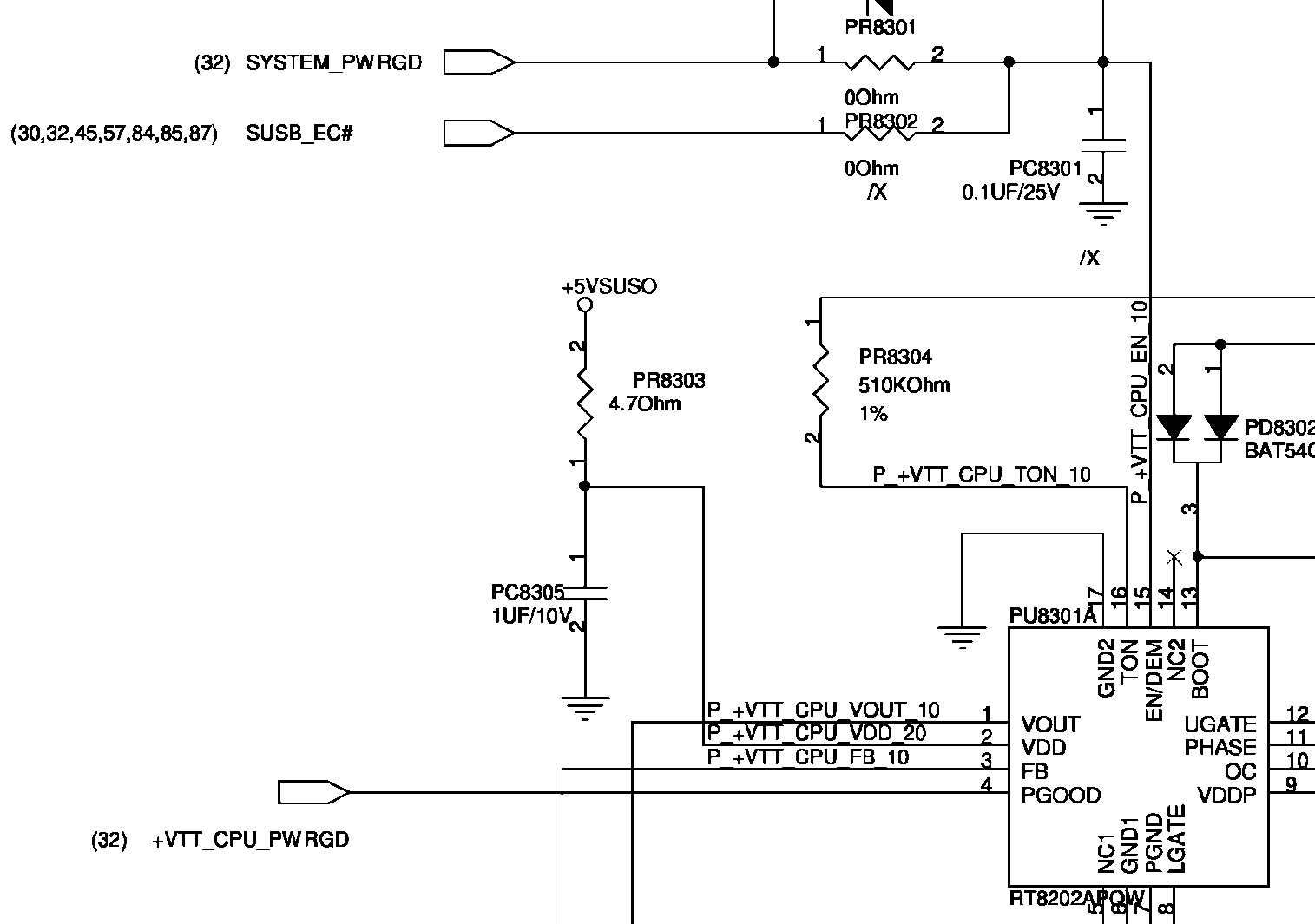

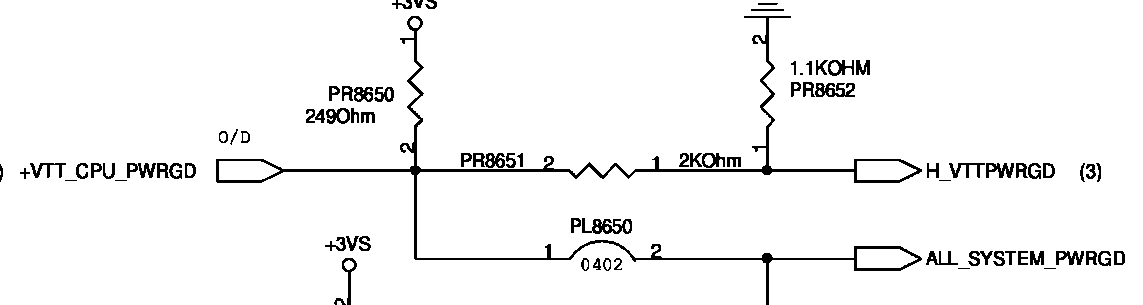

SYSTEM_PWRGD至RT8202(PU8301)开启+VTT_CPU、+VTT_PCH。电压产生正常后,芯片发出+VTT_CPU_PWRGD。

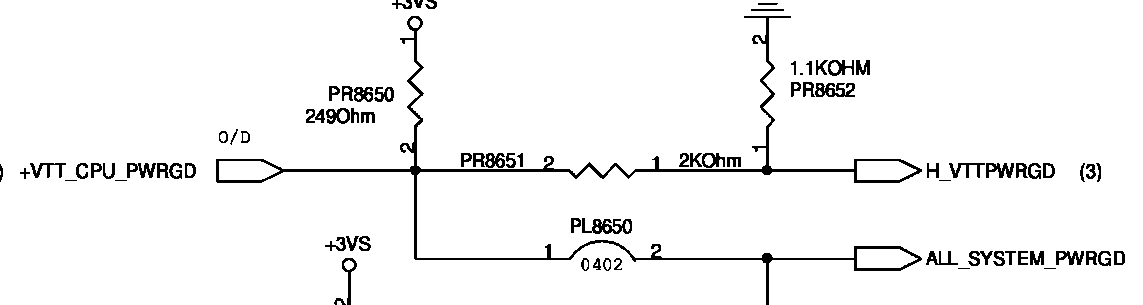

+VTT_CPU_PWRGD过电阻PR8651后更名为H_VTTPWRGD至CPU。

+VTT_CPU_PWRGD过电感PL8650更名为ALL_SYSTEM_PWRGD至EC。

+VTT_CPU_PWRGD过电感PL8650更名为ALL_SYSTEM_PWRGD至EC。

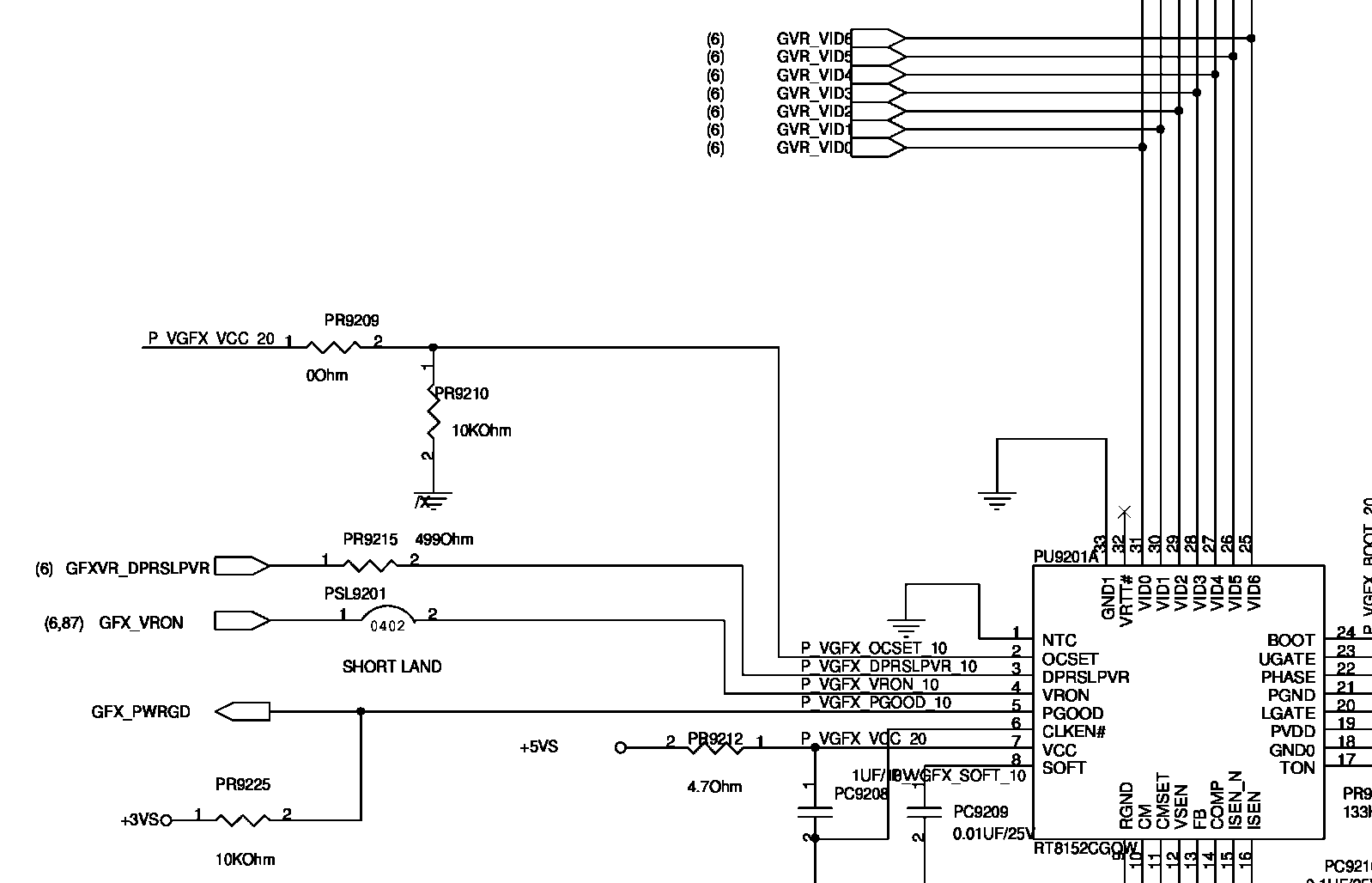

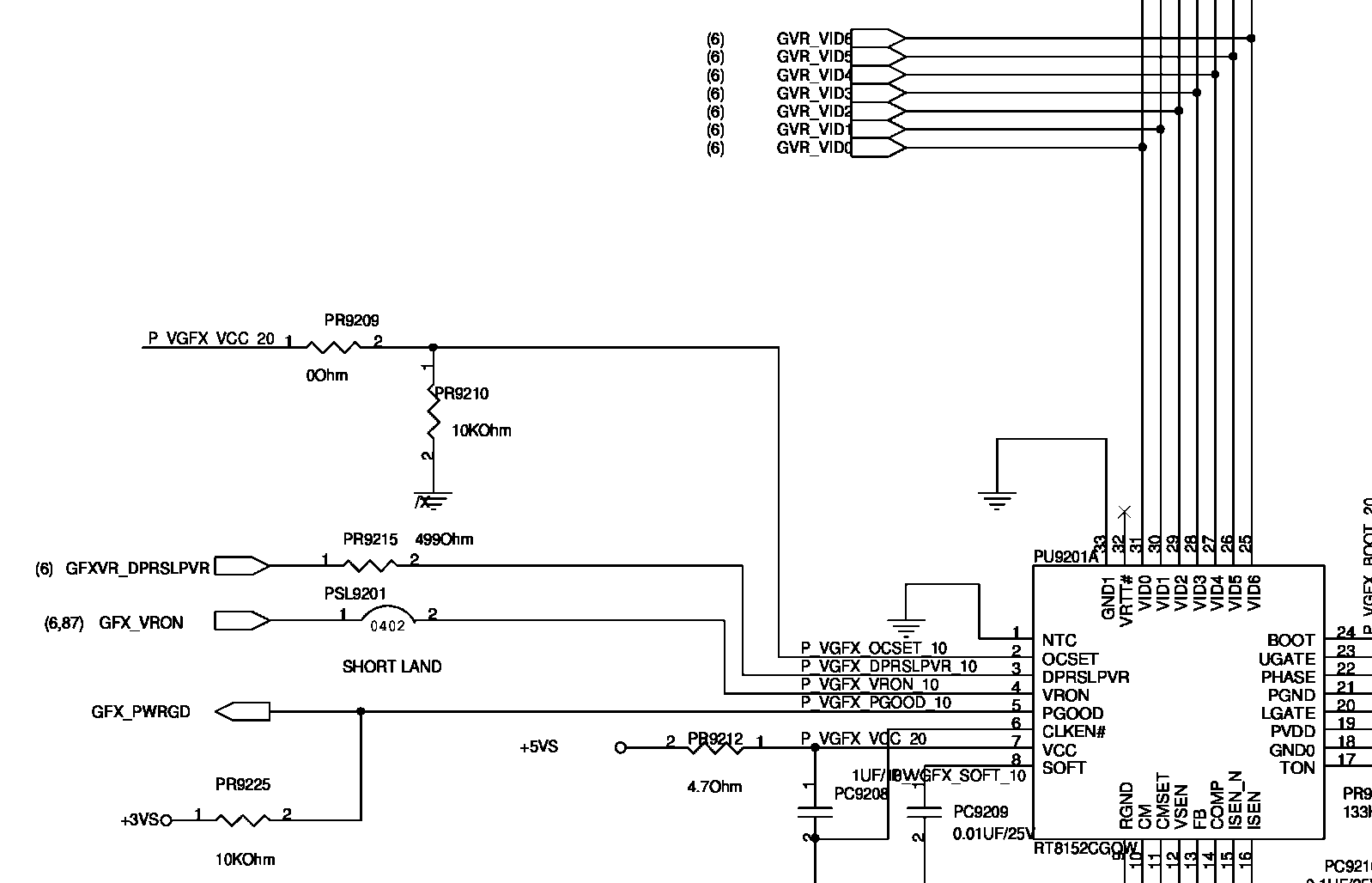

CPU得到+VTT_CPU和H_VTTPWRGD后,发出GFX_VRON及GFX_VID至RT8152(PU9201A),开启内置显卡的核心电压+VGFX_CORE。

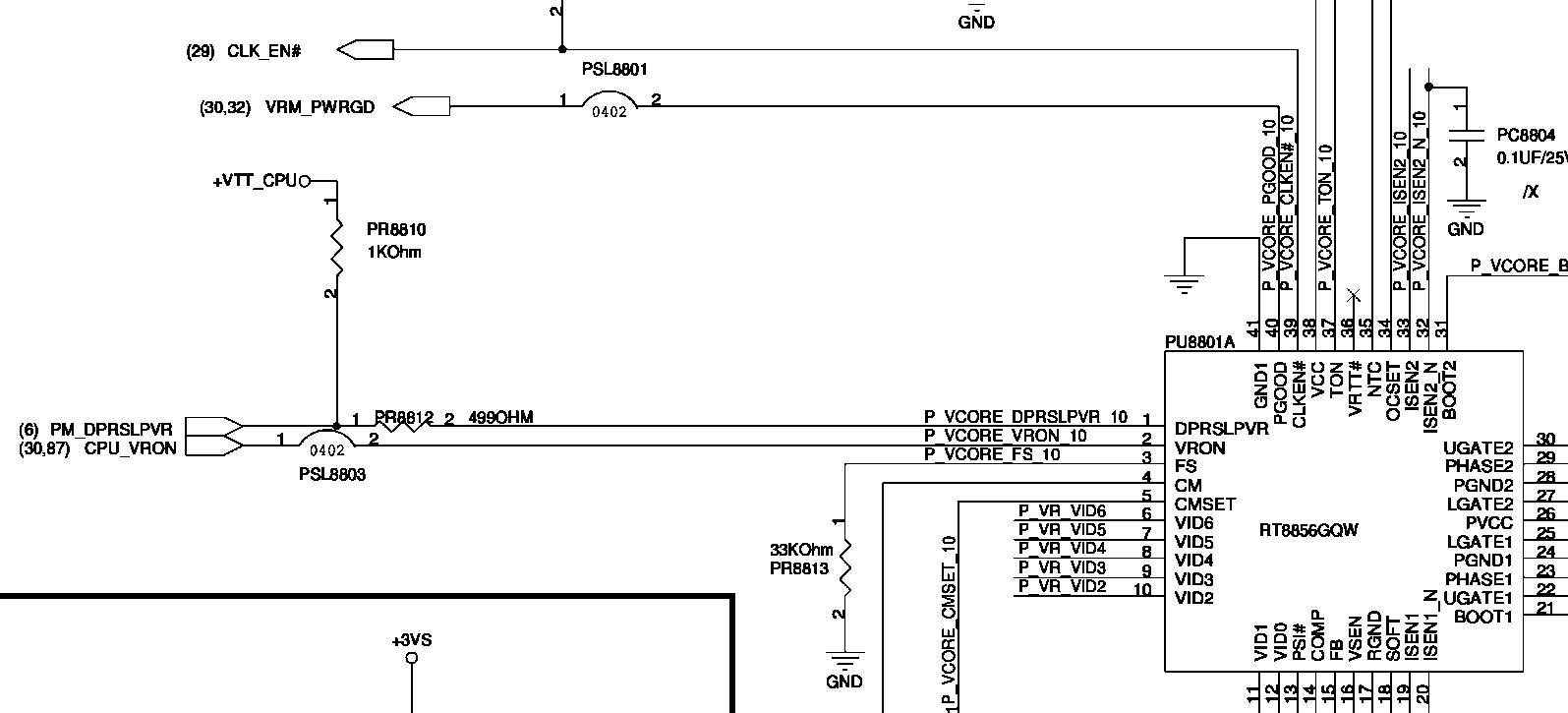

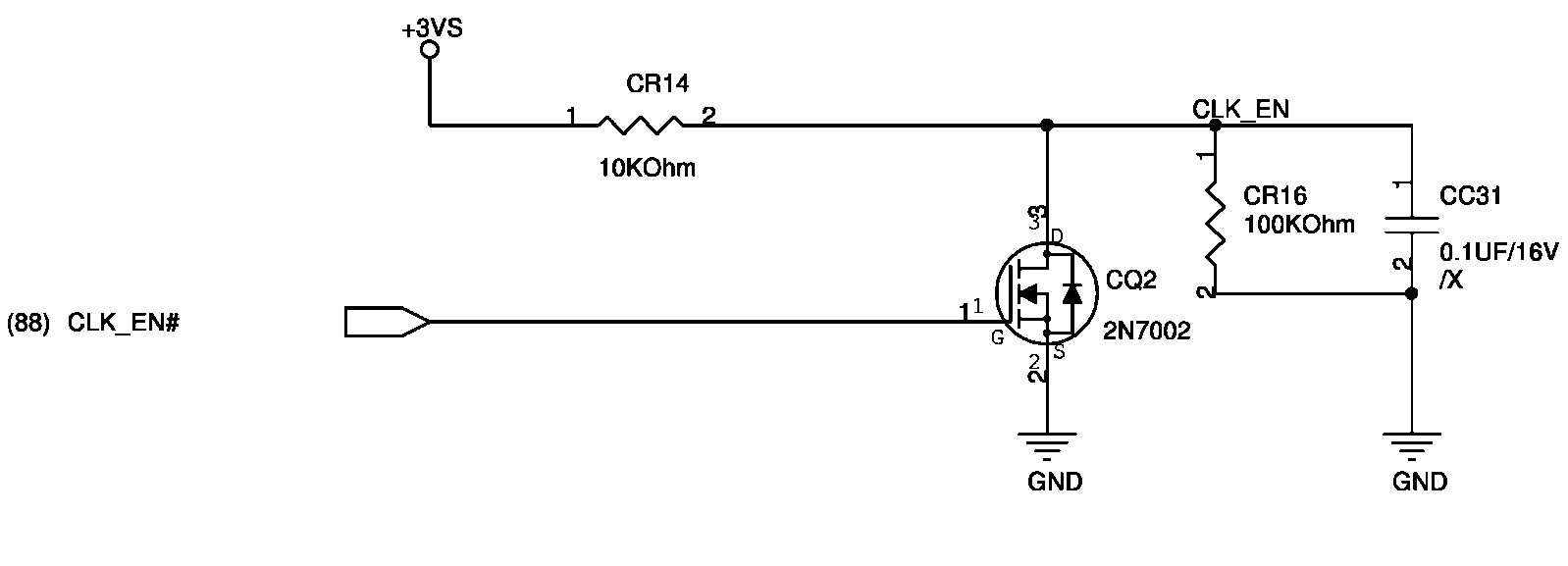

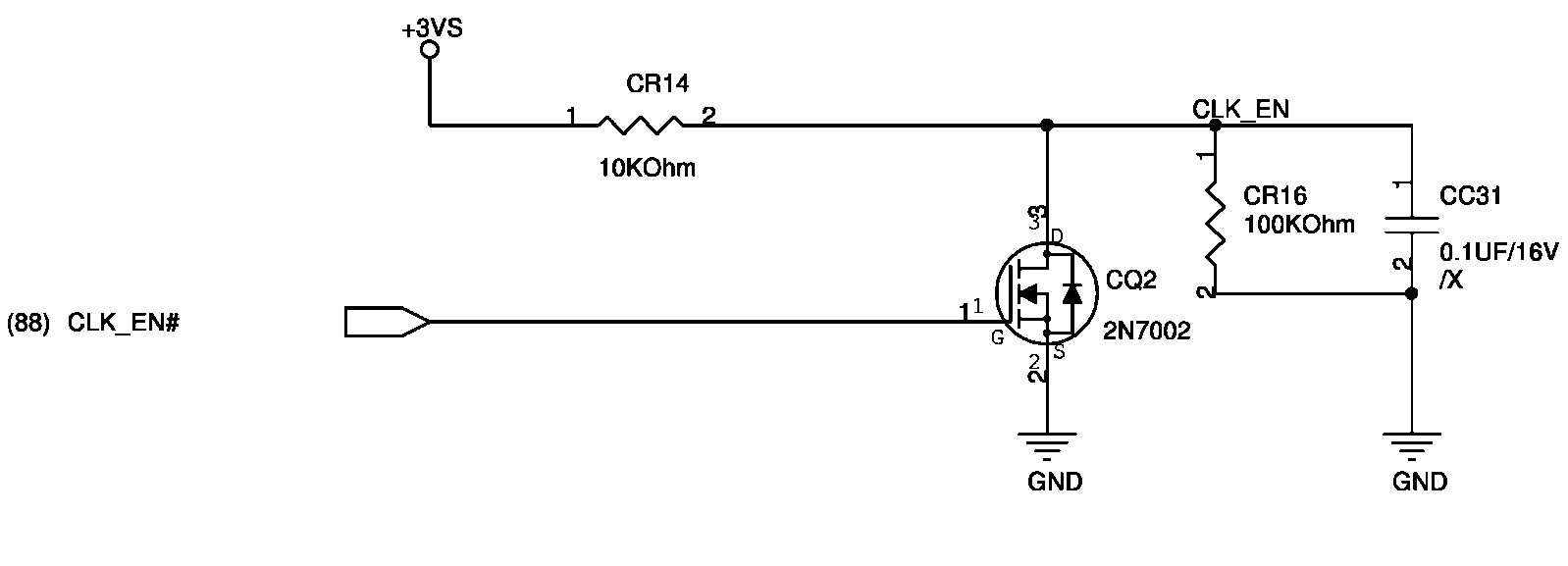

ALL_SYSTEM_PWRGD至EC后,EC延时99ms后发出CPU核心电压开启信号RT8856(PU8801A)开启+VCORE。+VCORE电压产生正常后,芯片输出VRM_PWRGD及CLK_EN#。

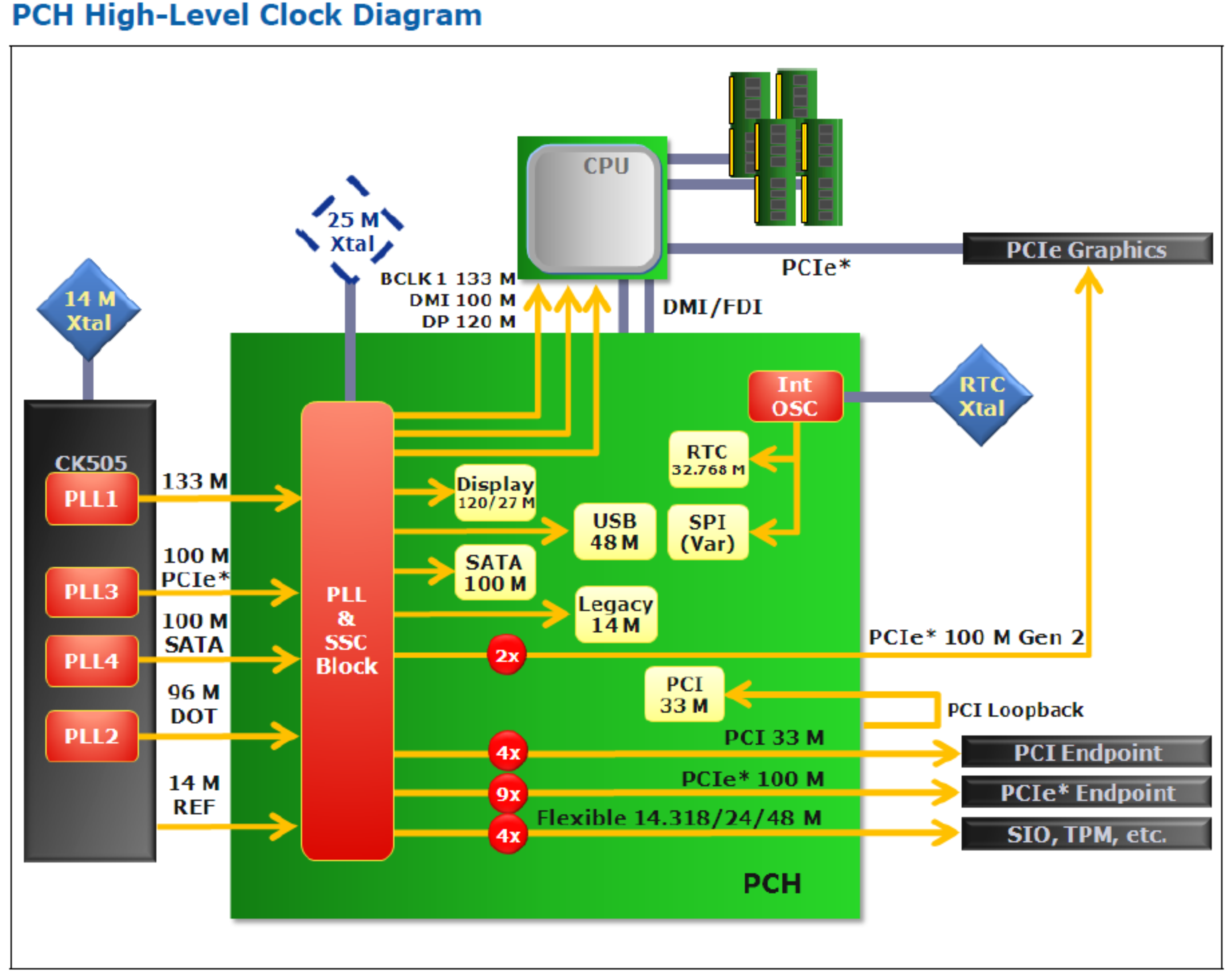

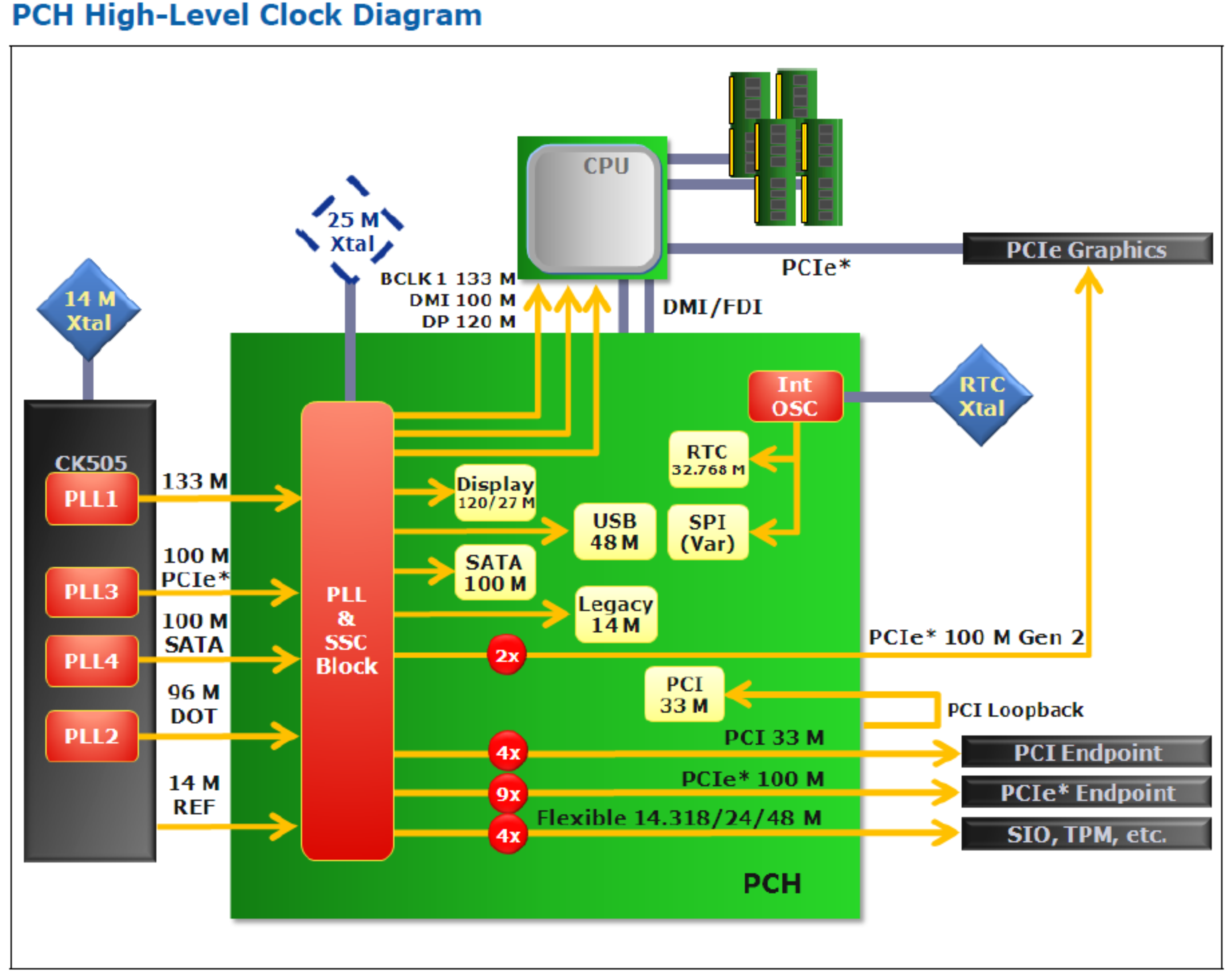

CLK_EN#经过CQ2反相成高电平,至时钟IC(ICS9LPRS427)开启时钟。

时钟IC开启工作后,产生各时钟至PCH,再由PCH内置时钟产生各时钟去往外设。

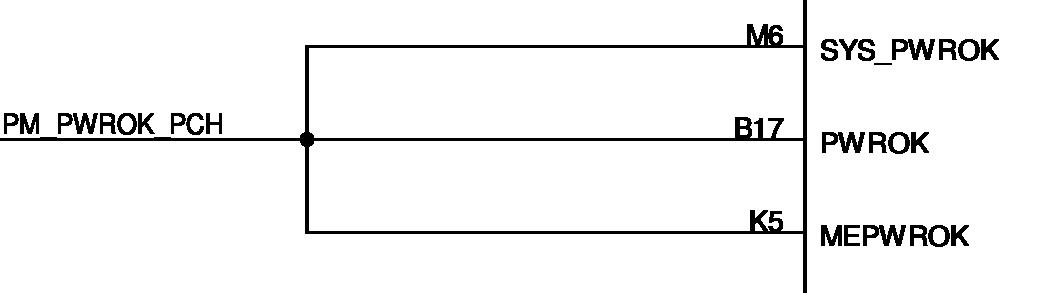

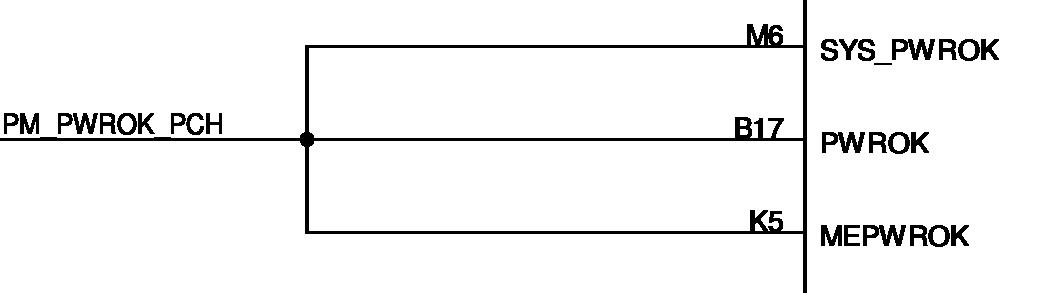

VRM_PWRGD至EC,EC延时发出PM_PWROK至PCH的MEPWROK、SYS_PWROK、PWROK脚。

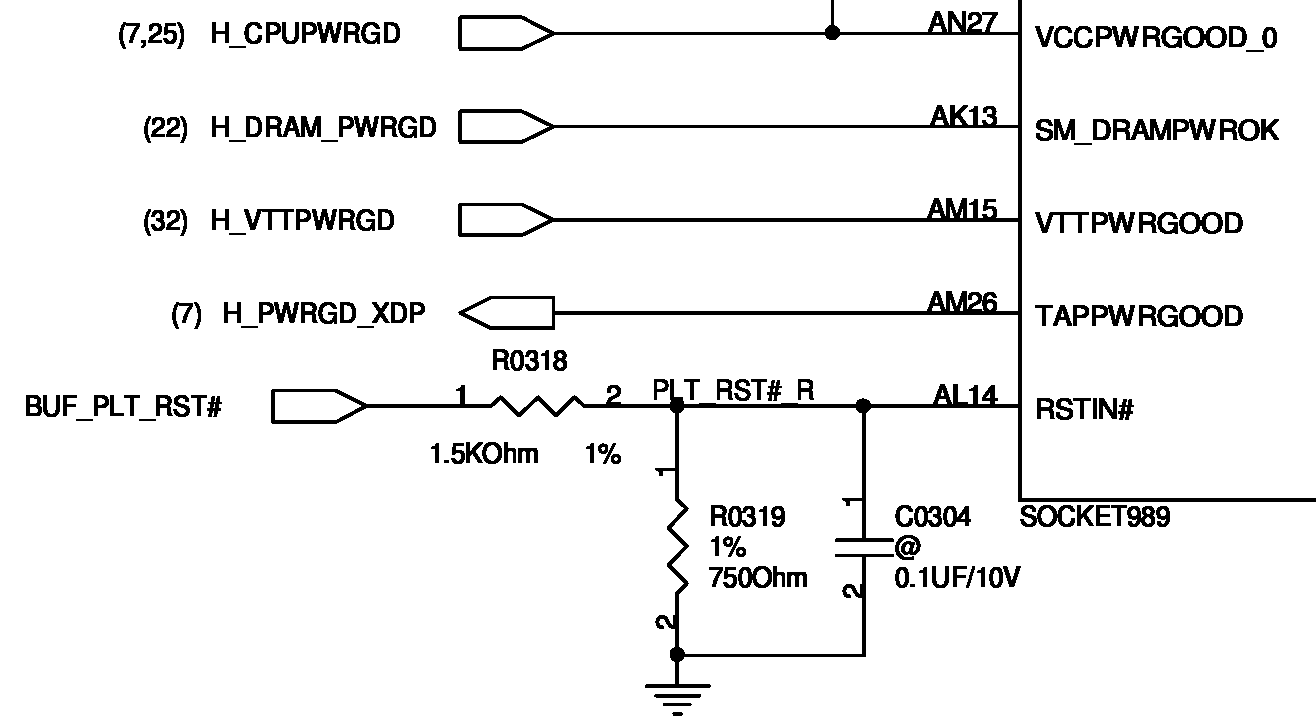

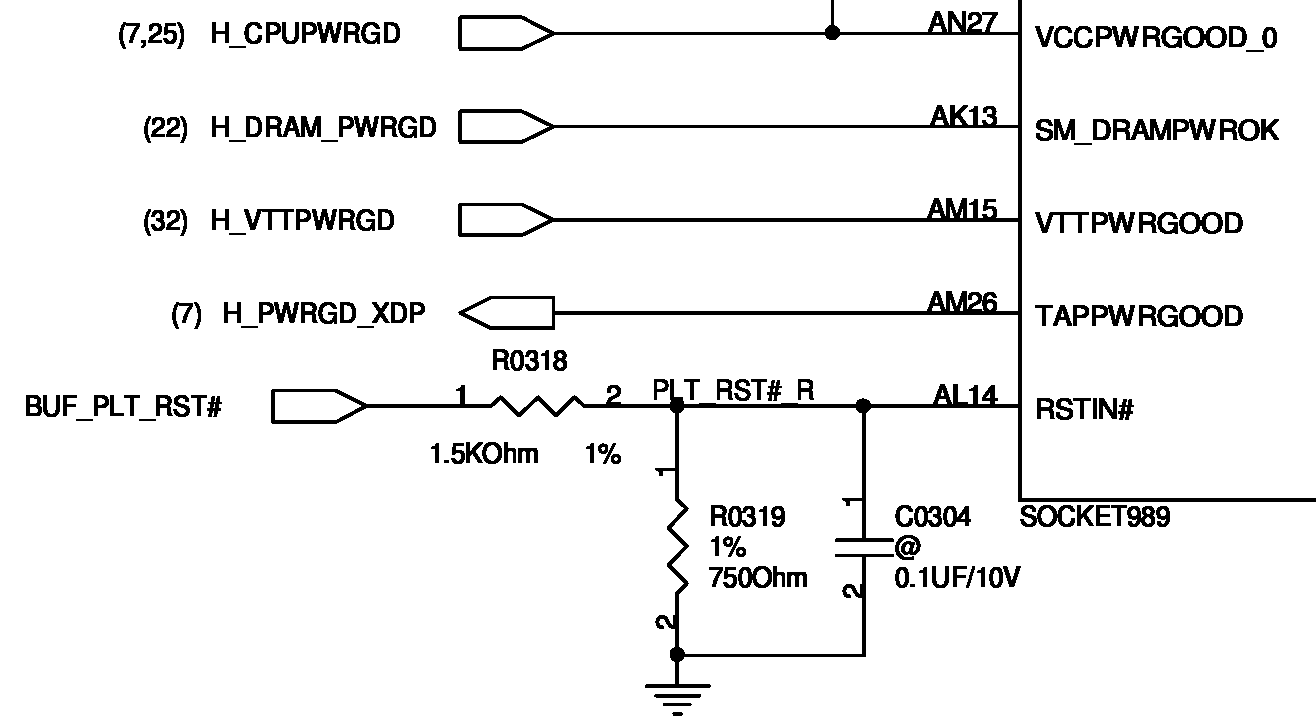

PCH收到PWROK后,发出DRAMPWROK信号至CPU。在PCH内部,PWROK及SYS_PWROK逻辑相与,产生PROCPWRGD至CPU。PCH发出PLTRST#更名为BUF_PLT_RST#经R0318、R0319分压成1.1V至CPU。

学到熟练维修 需要多少钱?

培训科目

培训科目

- 学校整体环境展示2022-10-18

- 选择迅维专业手机维修培训的十大理由2022-10-17

- 手机培训教室展示2022-10-16

- 学员实操维修台2022-10-15

- 笔记本维修培训教室展示2022-10-14

- 迅维培训软实力2022-10-13

- 迅维培训大量实操材料2018-07-06

- 迅维培训工具设施2018-07-06

网站快速导航

网站快速导航 联系方式

联系方式